| MARK 12                               | Installation/<br>Technical<br>Document |  |  |

|---------------------------------------|----------------------------------------|--|--|

|                                       |                                        |  |  |

|                                       |                                        |  |  |

|                                       |                                        |  |  |

|                                       |                                        |  |  |

|                                       | <b>N</b>                               |  |  |

|                                       |                                        |  |  |

| · · · · · · · · · · · · · · · · · · · |                                        |  |  |

•

Santa Santa Santa

2

# MARK 12 INSTALLATION/ TECHNICAL DOCUMENT

# June 10, 1986

## MARK 12 INSTALLATION/TECHNICAL DOCUMENT

#### PREFACE

This document contains interim information pertaining to the MARK 12 Computer. The material is drawn from technical memoranda, the MARK 8 Computer Reference Manual, the MARK 12 CPU Product Specification and engineering drawings.

This interim documentation will be replaced by formal documents for the MARK 12 which are now in process. They will include:

MARK 12 User's Guide MARK 12 Technical Reference Manual

# MARK 12 INTERIM DOCUMENTATION

# CONTENTS

| 1                                      | UNPACKING AND INSTALLATION<br>(MARK 12 Computer System Unpacking and Installation<br>Tech Memo)                                                                      | 1-1                                    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|                                        | Introduction<br>MARK 12 Computer System Components<br>Unpacking the MARK 12<br>System Installation                                                                   | 1-3<br>1-4<br>1-6<br>1-8               |

| 2A                                     | DIFFERENCES FROM MARK 5<br>(MARK 12 Computer System (Differences from MARK 5)<br>Tech Memo)                                                                          | 2A-1                                   |

|                                        | Introduction<br>Description of System Differences<br>Description of CPU Differences<br>LCM/Extended Memory Differences<br>CPU Status Word                            | 2A-2<br>2A-4<br>2A-6<br>2A-10<br>2A-11 |

| 2в                                     | MARK 12 CPU FUNCTIONAL DESCRIPTION<br>(excerpt from MARK 12 CPU Product Specification)                                                                               | 2B-1                                   |

| 2.1<br>2.2<br>2.3                      | General<br>MARK 12 CPU Signals<br>Programming                                                                                                                        | 2B-2<br>2B-2<br>2B-5                   |

| 3                                      | OPERATING PROCEDURES<br>(excerpt from MARK 8 Reference Manual)                                                                                                       | 3-1                                    |

| 3.1<br>3.2<br>3.3<br>3.4               | Introduction<br>Power Supply Indicator Panel<br>Processor Mini-Panel<br>(not applicable)                                                                             | 3-1<br>3-1<br>3-4                      |

| 3.5                                    | Virtual Control Panel<br>Processor/Cassette Tape Unit Interface                                                                                                      | 3-20<br>3-30                           |

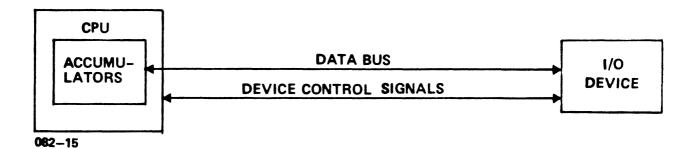

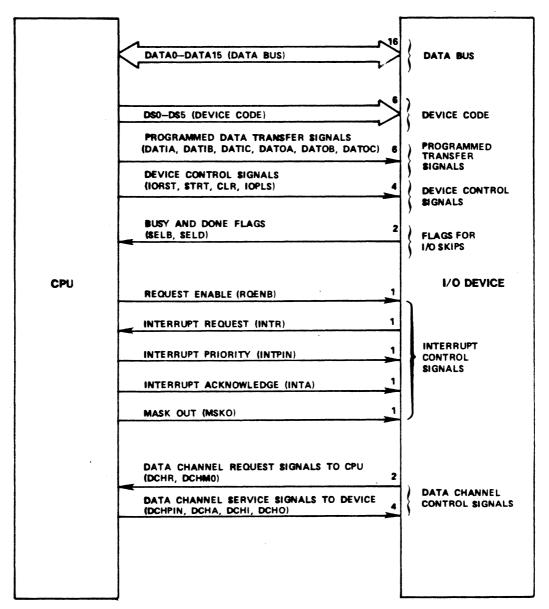

| 4                                      | INPUT/OUTPUT INTERFACES<br>(excerpt from MARK 8 Reference Manual)                                                                                                    | 4-1                                    |

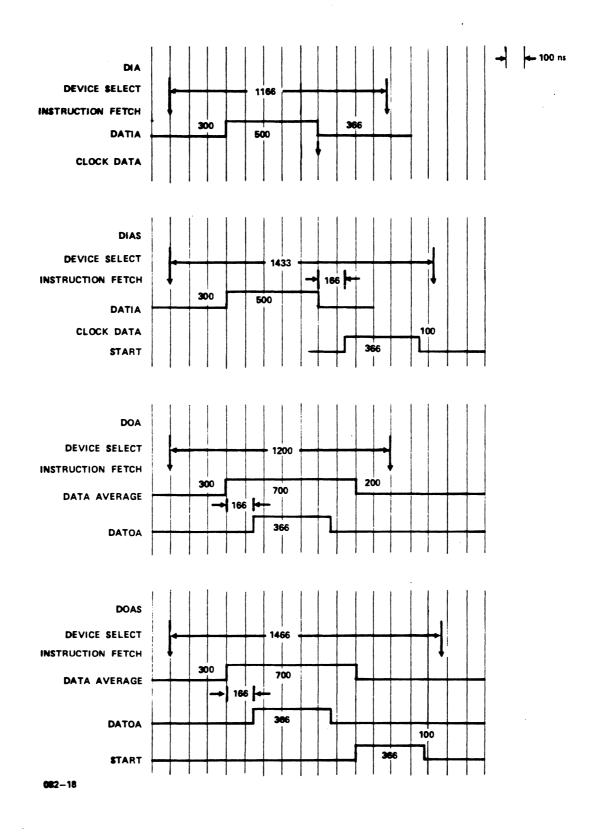

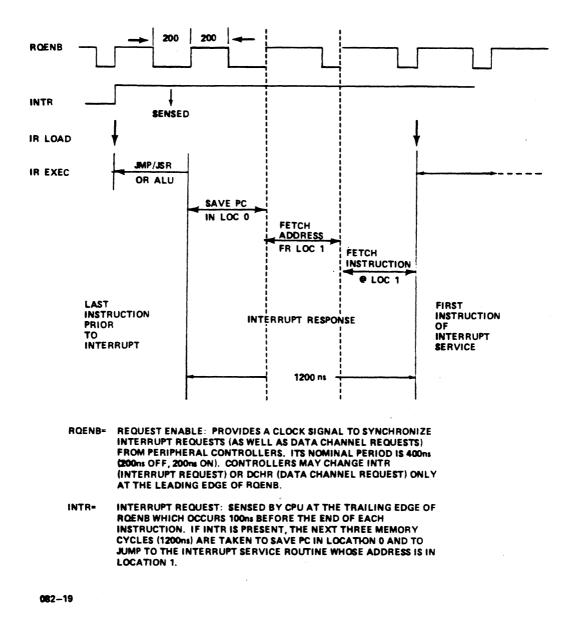

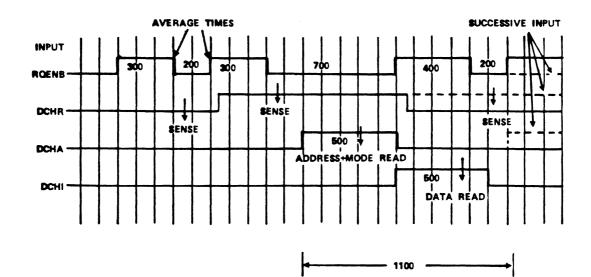

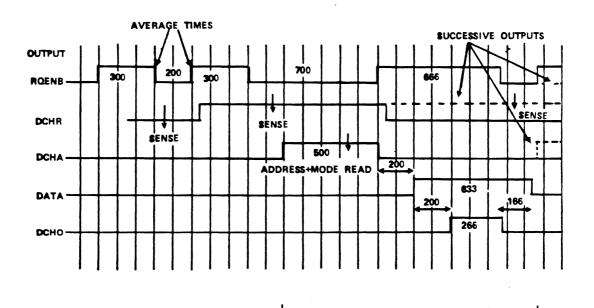

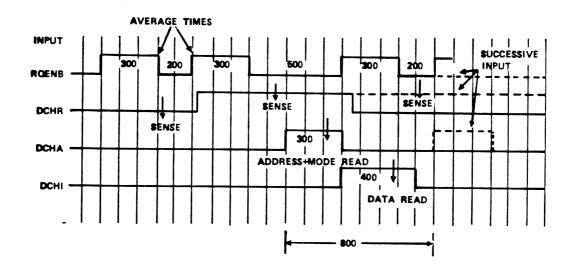

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction<br>Program Interrupt and Priority Scheme<br>Programmed Transfers<br>Data Channel Transfers<br>Input/Output Bus Interface Signals<br>Input/Output Timing | 4-1<br>4-3<br>4-6<br>4-8<br>4-18       |

iv

| 5   | STANDARD INSTRUCTION SET<br>(excerpt from MARK 8 Reference Manual) | 5-1  |

|-----|--------------------------------------------------------------------|------|

| 5.1 | Introduction                                                       | 5-1  |

| 5.2 | Octal Representation and Two's Complement Notation                 | 5-1  |

| 5.3 | Instruction Types                                                  | 5-3  |

| 5.4 | Memory Reference Instructions                                      | 5-5  |

| 5.5 | Arithmetic and Logical Instruction Group                           | 5-14 |

| 5.6 | Input/Output Instruction Group                                     | 5-26 |

#### APPENDICES

# (excerpts from MARK 8 Reference Manual)

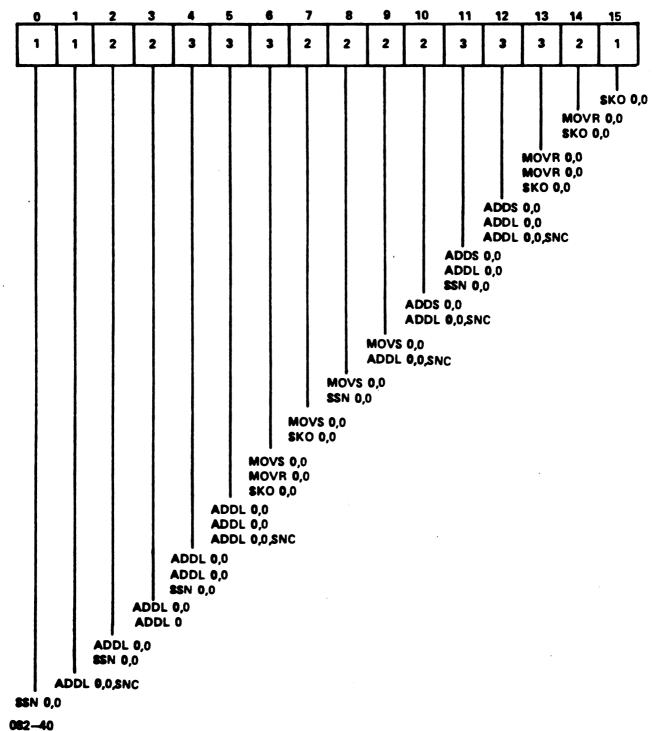

| A | Von Neumann Map of POINT 4 Instructions | A-1 |

|---|-----------------------------------------|-----|

| В | POINT 4 Instruction Reference Chart     | B-1 |

| С | ASCII Code Chart                        | C-1 |

| D | Virtual Front Panel Commands            | D-1 |

| Е | Programming Examples                    | E-1 |

# (from Engineering documents)

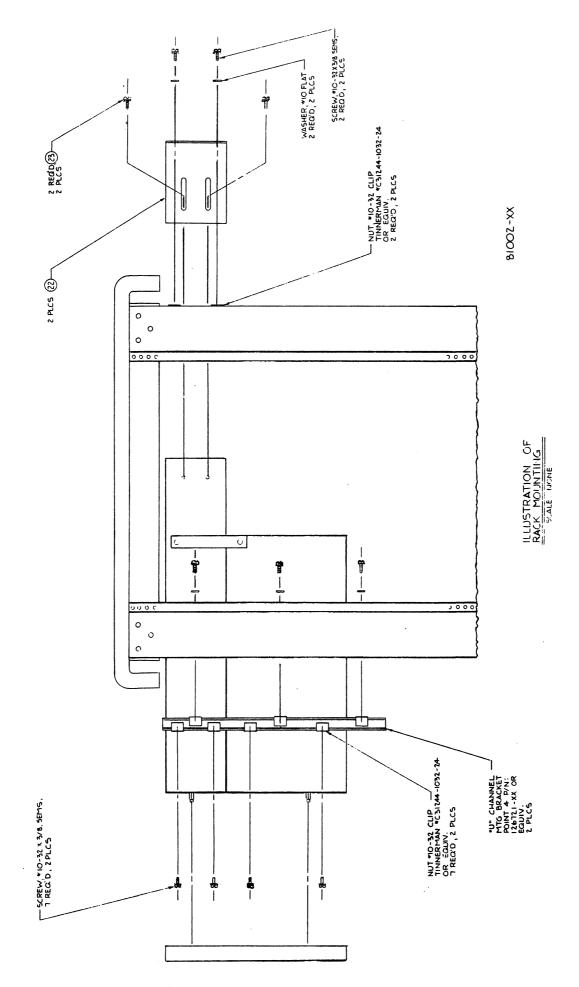

| F | MARK 1 | 2 Illustration of Rack Mounting | F-1 |

|---|--------|---------------------------------|-----|

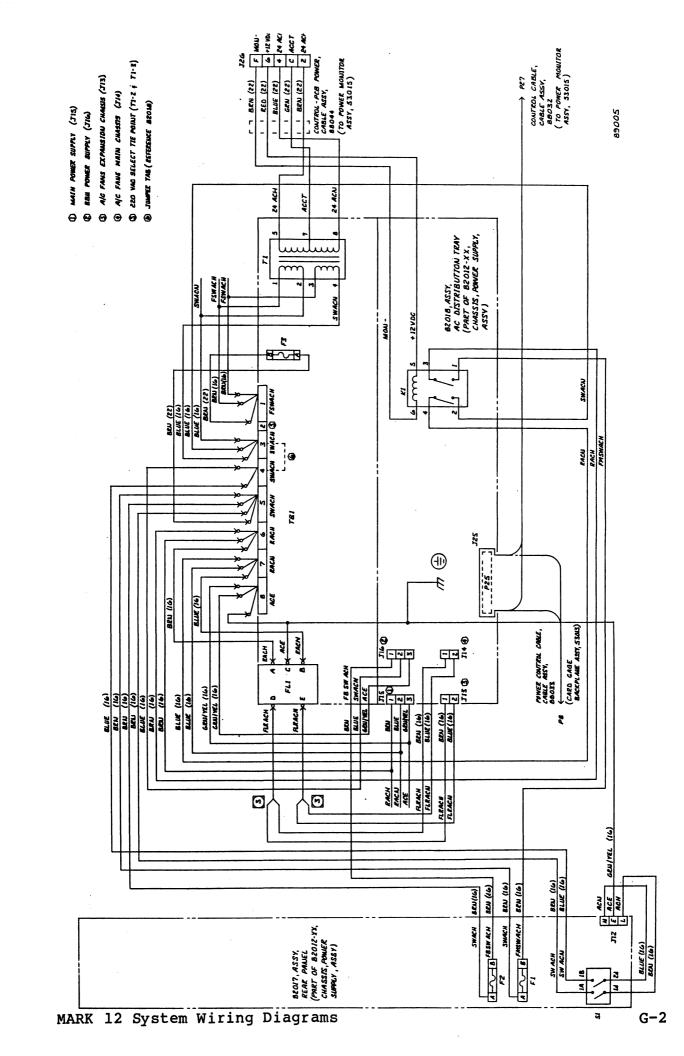

| G | MARK 1 | 12 System Wiring Diagrams       | G-1 |

| H | MARK 1 | 12 Backplane Board              | H-1 |

| I | MARK 1 | l2 Backplane Board Schematic    | I-1 |

-

V

. .

|       |                                       |      | 4444  |       |

|-------|---------------------------------------|------|-------|-------|

| POINT | 4 Data Corporation                    | 4    | 4444  | 4     |

|       | -                                     | 444  | 44    | 444   |

|       |                                       | 4444 | 4     | 4444  |

|       |                                       | 444  | 444   | 44444 |

|       |                                       | 4    | 44444 | 44444 |

|       | TECHNICAL                             |      |       |       |

|       | MEMORANDUM                            |      |       |       |

|       |                                       | 4444 | 44444 | 4444  |

|       | · · · · · · · · · · · · · · · · · · · | 444  | 44444 | 444   |

|       |                                       | 4    | 44444 | 4     |

| то:   | Installers of POINT 4 MARK 12 SYSTEMS |      | 4444  |       |

| FROM: | Tech Support                          |      |       |       |

DATE: June 10, 1986

SUBJ: MARK 12 COMPUTER SYSTEM UNPACKING AND INSTALLATION

This technical memo describes the POINT 4 MARK 12 Computer System and provides unpacking and installation procedures.

#### CONTENTS

Page

| I   | INTRODUCTION                       | 1-3 |

|-----|------------------------------------|-----|

| II  | MARK 12 COMPUTER SYSTEM COMPONENTS | 1-4 |

| III | UNPACKING THE MARK 12              | 1-6 |

| IV  | SYSTEM INSTALLATION                | 1-8 |

#### FIGURES

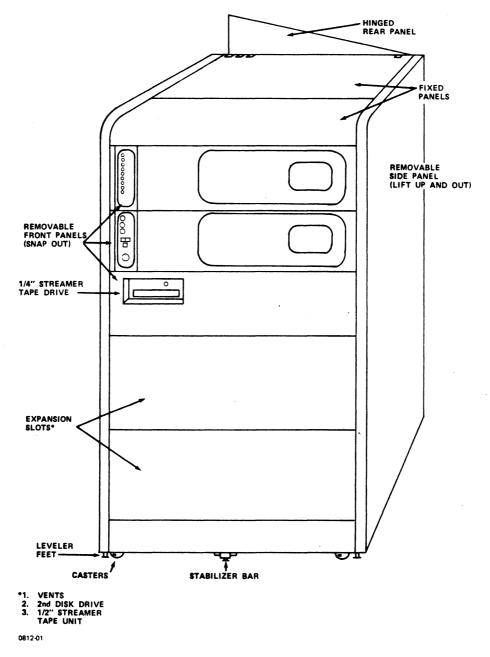

| 1 | MARK 12 Cabinet       | 1-3  |

|---|-----------------------|------|

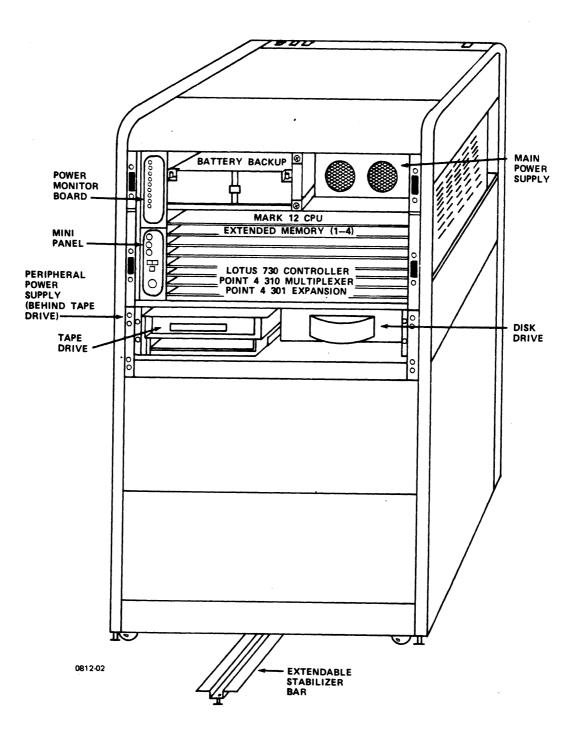

| 2 | MARK 12 Components    | 1-5  |

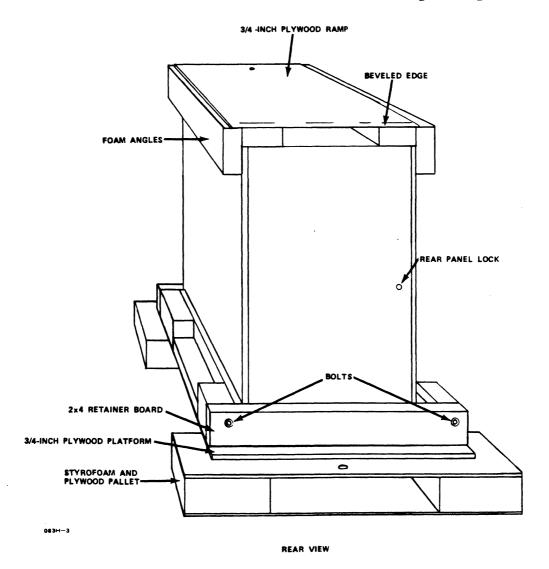

| 3 | MARK 12 Packaging     | 1-6  |

| 4 | Ramp Installation     | 1-7  |

| 5 | Rear View of Assembly | 1-10 |

#### APPENDICES

| Α         | MK12 CPU and Power Supply Inst | tallation  | 1-11 |

|-----------|--------------------------------|------------|------|

| POINT 4 N | NARK 12 Unpacking/Installation | , Rev 6/86 | 1-1  |

#### WARNING!

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference. Only shielded cables with the shield terminated to the metal hood of the connector should be used.

#### I. INTRODUCTION

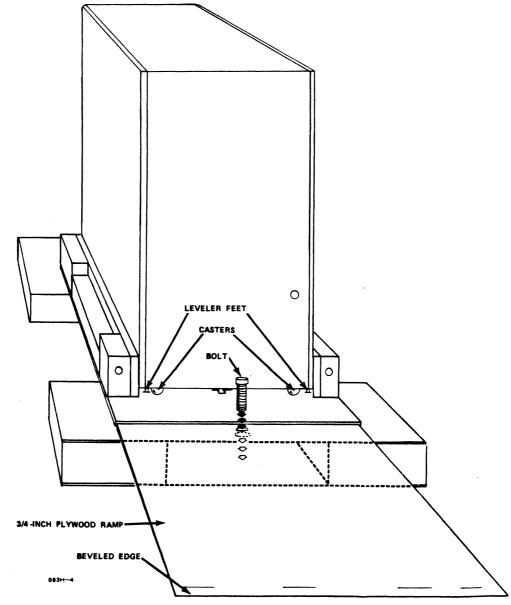

A fully-assembled POINT 4 MARK 12 Computer System is shipped in either a highboy cabinet (22 inches wide x 42 inches high x 30 inches deep) or a lowboy cabinet (22 inches wide x 31 inches high x 30 inches deep). The cabinet has four casters which allow it to be moved with ease, four preinstalled leveler feet, and a stabilizer bar to prevent the cabinet from tipping over (see Figure 1).

The system components are completely accessible by virtue of removable panels at the front and sides. The rear panel is hinged and can also be removed.

#### Figure 1. MARK 12 Cabinet

POINT 4 MARK 12 Unpacking/Installation, Rev 6/86

#### II. MARK 12 COMPUTER SYSTEM COMPONENTS

A full-configuration MARK 12 Computer System includes the following:

- A. Main power supply

- B. Computer chassis with the following boards:

- 1. MARK 12 CPU

- 2. Extended Memory (1-4 boards)\*

- 3. LOTUS 730 Controller

- 4. 1/2-inch Streamer Tape Controller\*\*

- 5. POINT 4 310 Multiplexer

- 6. POINT 4 301 Expansion Board

- 7. LOTUS Cache Memory (LCM)\*

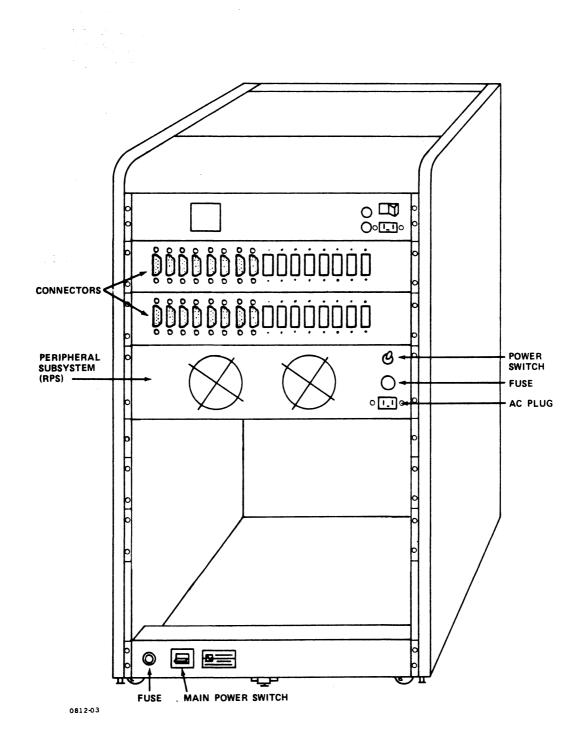

C. Rack-Mounted Peripheral Subsystem (RPS) with the following:

- 1. 8-inch Disk Drive

- 2. Peripheral Power Supply Unit

- 3. QIC-02 1/4-inch Streamer Tape Drive\*\*

- D. Optional Second Disk Drive

- E. 1/2-inch Streamer Tape Drive\*\*

\*The extended memory boards and LCM are optional. A system may not include both types of boards.

\*\*Each system is supplied with one streamer tape drive, either for 1/4-inch or 1/2-inch tape. The 1/4-inch tape drive is included in the RPS and is controlled by the LOTUS 730. The 1/2-inch tape drive is on a separate panel and requires a controller in the main chassis.

# Figure 2. MARK 12 Components

.

#### III. UNPACKING THE MARK 12

The MARK 12 is shipped on a wooden pallet and is held firmly in place by four 2x4 retainer boards (three fixed and one removable). The unit is protected by styrofoam angles and a plywood board that doubles as a ramp. The assembly is covered by a cardboard carton (or a wooden crate for delivery outside the United States) held in place by straps. An Allen key is taped to the rear panel.

The recommended procedure for unpacking the MARK 12 is as follows:

- 1. Remove the straps.

- 2. Lift off the cardboard cover (or wooden crate).

- 3. Unbolt the removable 2x4 retainer board (see Figure 3). One of the bolts will be used to secure the ramp (step 5).

Figure 3. MARK 12 Packaging

- 4. Remove the plywood ramp and styrofoam protectors from the top of the unit.

- 5. Place the ramp on the pallet so that the hole in the ramp lines up with the hole in the pallet. Insert one of the bolts taken from the retainer board in step 3 through both holes (see Figure 4).

- 6. Make sure that the leveler feet are clear of the pallet and cannot impede the rollers. Roll the unit down the ramp.

- 7. Move the unit close to its permanent place which should allow access to the sides and rear of the unit.

- 8. Store the pallet, ramp, and other packing material in a safe place.

Figure 4. Ramp Installation

#### **IV. SYSTEM INSTALLATION**

The POINT 4 MARK 12 Computer System is shipped fully assembled and no additional cabling is required. The recommended installation procedure is as follows:

- 1. Pull out the stabilizer bar at the front of the unit to prevent it from tipping over.

- Snap out the removable front panels (i.e., the panels covering the main power supply, the computer chassis, and the RPS).

- 3. Check each board in the computer chassis as follows:

- a. Slide the board out by pulling out on the metal tabs.

- b. Remove the packing from around the board.

- c. Check that the board components are firmly seated.

- d. Using the metal tabs, slide the board back into place.

- 4. Make sure all cables are connected.

- 5. Snap the front panels back into place.

- 6. Detach the Allen key from the rear panel. Unlock the panel by inserting the key and turning it counterclockwise. (The rear panel may be removed entirely by first detaching the green ground wire and then pulling down on the spring hinge. When replacing the rear panel, make sure that the ground wire is reconnected.)

- 7. Check the plug and fuse on the main power supply; make sure that the switch above them is turned to the ON position.

- 8. Check the connectors on the main power supply unit; make sure they are firmly seated.

- 9. If the Battery Backup (BBU) option is installed, remove the battery tray and plug the battery cable into connector J5 on the BBU board.

- 10. Check the fuse on the rear of the RPS; make sure the plugs are firmly seated and the power switch is turned to the ON position.

- 11. IRIS users make sure the Pico-N is installed on the backplane.

- 12. Plug CRT and printer cables into the multiplexer connector panel at the back of the unit (the first connector is the leftmost one).

POINT 4 MARK 12 Unpacking/Installation, Rev 6/86

- 13. Plug the unit into the main AC power (3-pronged, grounded wall outlet). General power is controlled by a lighted on/off button at the rear of the unit (see Figure 5). If it does not light up when the unit has been connected to the main power outlet, press the button; the light should come on.

- 14. Close the rear panel (make sure the cables extend freely through the bottom of the door; the ground wire must be reconnected if the panel was removed entirely).

- 15. Push the stabilizer bar back so that it does not extend beyond the cabinet.

- 16. Move the unit to its permanent place.

- 17. Lower the leveler feet by turning them counterclockwise until the rollers are lifted off the floor.

- 18. Adjust the leveler feet so that the unit is level.

- 19. To install software, see the IRIS R8 Installation and Configuration Manual and the IRIS R8 Release Notes.

Figure 5. Rear View of Assembly

POINT 4 MARK 12 Unpacking/Installation, Rev 6/86

#### Appendix A

#### MARK 12 CPU AND POWER SUPPLY INSTALLATION

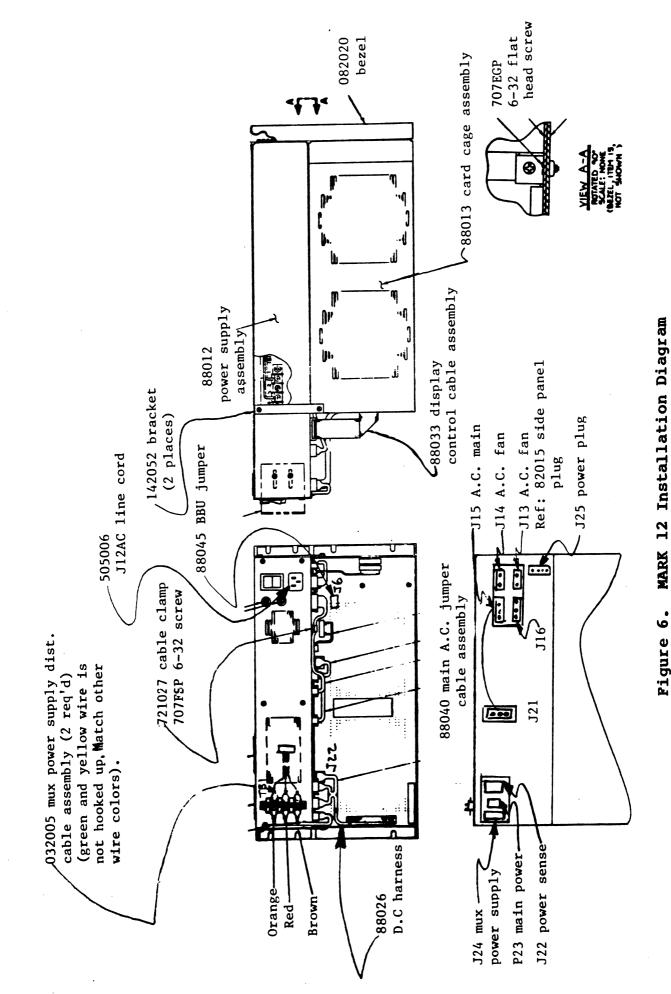

The following are mechanical and electrical hook-up instructions for installing a MARK 12 CPU card cage and power supply in a non-POINT 4 cabinet. See Table 1 for a list of the parts contained in the MARK 12 shipping kit.

- A. Mechanical Installation

- Install (2) chassis; 88012 power supply on top of 88013 card cage per Figure 6.

- 2. Install per Figure 6:

- (2) 142052 bracket supports

- (4) 707FSP 8-32 x 3/8 flat head screws

- (1) 712202 **#6** washers

- (1) 707D6P #6 1/4" flat head screw

- (2) 142061 bracket

- 3. Install per Figure 6 (required for UL conformity):

- (1) 721027 cable clamp

(1) 707FSP screw

- 4. (12) 709HSP 10-32 x 1/2 phillips head sems screws are available for MARK 12 assembly-to-console installation.

- 5. Install 082020 bezel assembly.

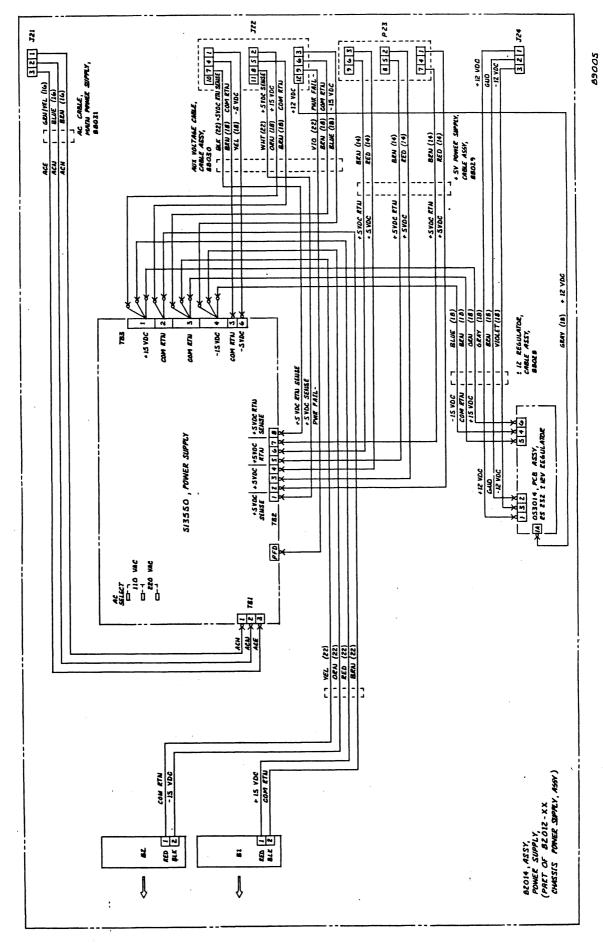

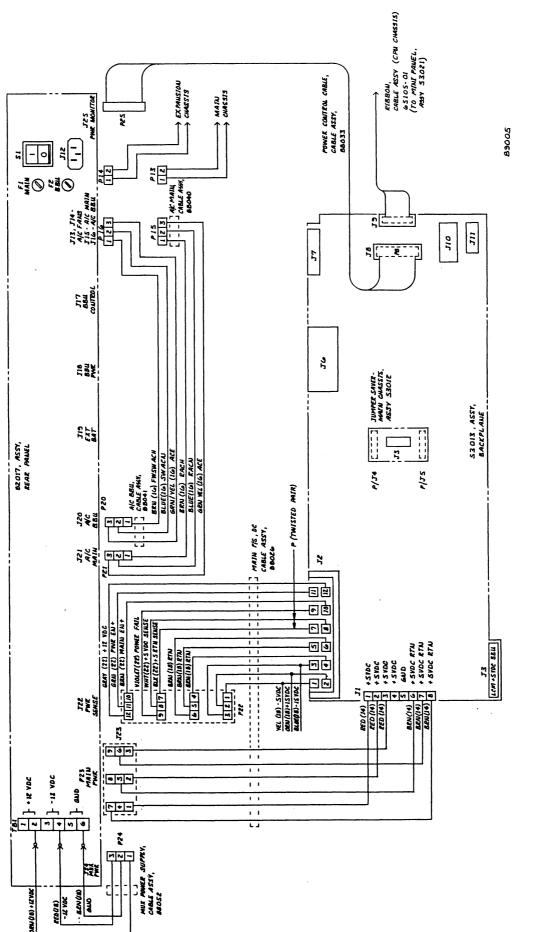

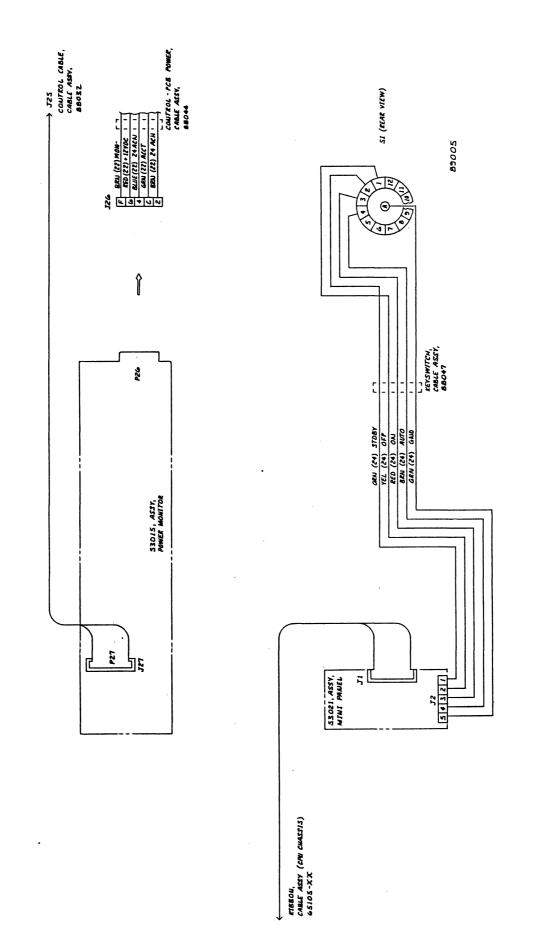

- B. Electrical Installation MARK 12 Cable Interconnects

Connect the cables between the MARK 12 card cage and power supply according to the following and Figure 6:

|      |                                                                                                                   | FROM                          | то                                     |

|------|-------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|

| 1.   | Loose cables in P/N 099001<br>MKl2 shipping kit:                                                                  |                               |                                        |

|      | (1) 088045 BBU jumper                                                                                             | P/S J21<br>C/C J 6<br>P/S J12 |                                        |

|      | <ol> <li>(1) 088052 cable assy. mux pwr.</li> <li>(2) 032005 mux power supply<br/>dist. cable assembly</li> </ol> |                               |                                        |

| 2.   | Cables on end to connect:                                                                                         |                               |                                        |

|      | (1) 88026 DC harness                                                                                              | C/C<br>C/C                    | P/S J22 pwr. sen.<br>P/S P23 main pwr. |

|      | <ul><li>(2) 88033 display control</li><li>(3) 82015 side panel assy.</li></ul>                                    | C/C J8<br>C/C                 |                                        |

| whei | ce<br>C/C = card cage assembly 82012<br>P/S = power supply asembly 8201                                           | 3                             |                                        |

POINT 4 MARK 12 Unpacking/Installation, Rev 6/86

| PART NO. | DESCRIPTION                 |    | QUANTITY |    |    | REMARKS |

|----------|-----------------------------|----|----------|----|----|---------|

|          |                             |    |          |    | 04 |         |

| 707 FSP  | SCREW 6-32 x 3/8 PHIL.      | 1  |          |    | 1  |         |

| 721027   | CLAMP CABLE 3/8 DIA.        | 1  | 1        | 1  | 1  |         |

| 082020   | BEZEL ASSEMBLY              | 1  | 1        | 1  | 1  |         |

| 141052   | BRACKET SUPPORT             | 2  | 2        | 2  | 2  |         |

| 107 EGP  | SCREW 6-32 x FLAT HEAD      | 5  | 5        | 5  | 5  |         |

| 709 HSP  | SCREW 10-32 x 1/2 PHIL HD   | 12 | 12       | 12 | 12 |         |

| 142061   | BRACKET                     | 2  | 2        | 2  | 2  |         |

| 708 FSP  | 8-32 x 3/8 SEMS PHIL HD     | 4  | 4        | 4  | 4  |         |

| 712240   | <b>‡10 FLAT WASHER</b>      | 1  | 1        | 1  | 1  |         |

| 088040   | CA. ASSY. MAIN A/C JUMPER   | 1  | 1        | 1  | 1  |         |

| 088041   | CA. ASSY. BBU A/C JUMPER    | -  | -        | 1  | 1  |         |

| 088035   | CA. ASSY. BBU CONTROL       | -  | -        | 1  | 1  |         |

| 088036   | CA. ASSY. BBU D/C PWR. SUP. | -  | -        | 1  | 1  |         |

| 505006   | A/C LINE CORD               | 1  | 1        | 1  | 1  |         |

| 088045   | CA. ASSY. BBU JUMPER        | 1  | 1        | -  | -  |         |

| 088052   | CA. ASSY. MUX POWER         | 1  | 1        | 1  | 1  |         |

| 032005   | CA. ASSY. MUX P/S DIST.     | 2  | 2        | 2  | 2  |         |

# TABLE 1. MARK 12 SHIPPING KIT, P/N 099001

#### LEGEND:

| 099001-01 | 115 | VAC |      |     |

|-----------|-----|-----|------|-----|

| 099001-02 | 230 | VAC |      |     |

| 099001-03 | 115 | VAC | WITH | BBU |

| 099001-04 | 230 | VAC | WITH | BBU |

POINT 4 MARK 12 Unpacking/Installation, Rev 6/86

---

|            |       | 4444   |       |

|------------|-------|--------|-------|

| on         | 44444 |        | 4     |

|            | 444   |        | 444   |

|            | 4444  | 4      | 4444  |

|            | 444   | 444    | 44444 |

|            | 4     | 44444  | 44444 |

| TECHNICAL  |       |        |       |

| MEMORANDUM |       |        |       |

|            |       | 444444 | 4444  |

|            | 444   | 444444 | 444   |

|            | 4     | 444444 | 4     |

|            |       | 4444   |       |

- ----

MARK 12 Users TO:

FROM: Hardware Development

DATE: June 10, 1986

SUBJ: MARK 12 COMPUTER SYSTEM (Differences from MARK 5)

This tech memo includes a description of the features of the MARK 12 computer system and describes the MARK 12 in terms of additions or deviations from the MARK 5 computer system.

#### CONTENTS

| I.                       | INTRODUCTION                                                                                                    | 2A-2                                         |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.2                      | SYSTEM FEATURES<br>CPU FEATURES<br>EXTENDED MEMORY FEATURES<br>OPTIONS                                          | 2A-2<br>2A-2<br>2A-3<br>2A-3                 |

| 11.                      | DESCRIPTION OF SYSTEM DIFFERENCES                                                                               | 2A-4                                         |

| 2.2<br>2.3<br>2.4<br>2.5 | POWER<br>BATTERY BACKUP OPTION<br>DATA CHANNEL<br>DEVICE CODES 2 AND 3<br>EXTENDED INSTRUCTION SET<br>BACKPLANE | 2A-4<br>2A-4<br>2A-5<br>2A-5<br>2A-5<br>2A-5 |

| III.                     | DESCRIPTION OF CPU DIFFERENCES                                                                                  | 2A-6                                         |

|                          | CPU STATUS LEDS<br>SELF-TESTING CAPABILITIES<br>MANIP - VIRTUAL CONTROL PANEL                                   | 2A-6<br>2A-7<br>2A-9                         |

| IV.                      | LCM/EXTENDED MEMORY DIFFERENCES                                                                                 | 2A-10                                        |

| 4.1<br>4.2               | LCM<br>EXTENDED MEMORY                                                                                          | 2A-10<br>2A-10                               |

| r.                       | APPENDICES                                                                                                      |                                              |

| A-1. |

|------|

| ł    |

MARK 12 Computer System, Rev 6/86

2A-1

#### I. INTRODUCTION

A MARK 12 Computer System consists of an 8-slot card cage, a power supply, and a MARK 12 CPU with optional extended memory. The MARK 12 is a 16-bit industry-standard CPU with 128K bytes of onboard static RAM. The MARK 12 can access up to 16MB of external memory located on up to four MARK 12 memory expansion boards, each containing from 2 to 4MB.

The MARK 12 is an extension of the POINT 4 MARK 5/8/9 product line. It is functionally equivalent to the MARK 5 except as described herein.

#### **1.1 SYSTEM FEATURES**

- Basic Unit 8-card CPU chassis and power supply chassis (10.5-inch total rack space)

- Modular design for main power supply and battery backup (for extended memory or LCM) including Mux power supply (without current loop)

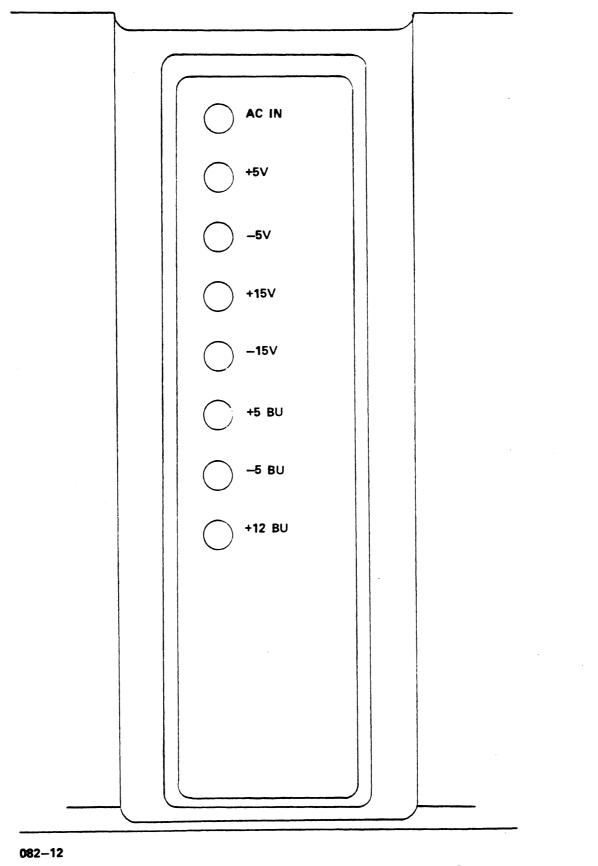

Main P/S: +5V, +15V, -15V, -5V, +12V, -12V BBU P/S: +5V, +12V, -5V

- Powerfail backup capability when used with extended memory (will be available with the release of IRIS 8.4)

- Power option for 8 additional card slots

- Increased air flow for better cooling

- Designed to safety requirements of UL, CSA, VDE

#### **1.2 CPU FEATURES**

The following are additions or deviations from the MARK 5:

- 64-nanosecond effective cycle time

- Up to 16 megabytes of extended memory, packaged at up to 4 megabytes per board

- Variable size pages any multiple of 8 bytes

- 32-bit high-speed bus accessing 16-megabyte extended memory

- Expanded Self-Test and MANIP

- Firmware-level hardware-verify and Virtual Control Function

- 3 software modes: 32KW-addressing (Nova\*), 64KW-addressing (MARK 5), MARK 12

\*Nova is a registered trademark of Data General Corp.

#### **1.3 EXTENDED MEMORY FEATURES**

The following are functional differences from the LCM:

- High-speed, 32-bit bus to the CPU

Data rate 33.3 megabytes-per-second burst transfer rate

- 2 and 4-megabyte boards with Error Detection and Correction (EDAC)

- Full battery backup option for LCM or Extended Memory only; does not backup 128KB onboard memory)

#### 1.4 OPTIONS

#### System

The MARK 12 Battery Backup (BBU) Option will provide backup power to the Extended Memories and both old and new POINT 4 LCMs with the release of IRIS 8.4.

The Auxiliary Chassis provides 8 additional slots for system expansion. Power is provided by the main power supply. The combined power capabilities of the Main and BBU supplies can power most configurations.

#### CPU

The Universal (Switch/Indicator) option available for MARK 5/9 CPUs is standard on the MARK 12.

MARK 12 Computer System, Rev 6/86

#### **II. DESCRIPTION OF SYSTEM DIFFERENCES**

#### 2.1 POWER

#### Input Power

115V operation - 90-132V 50/60 Hz 230V operation - 180-264V 50/60 Hz

#### Output Power

The MARK 12 power supply provides additional current; a separate Mux power supply is no longer required.

| +5V          | 50 | amps  |

|--------------|----|-------|

| <u>+</u> 15V |    | amps* |

| <u>+</u> 12V | 3  | amps  |

| -5V          | 5  | amps  |

\*Total of 15V and 12V currents not to exceed 5 amps

#### 2.2 BATTERY BACKUP OPTION

The MARK 12 Battery Backup Option when available, will provide backup power to the Extended Memories and both old and new POINT 4 LCMs. The onboard memory of the MARK 12 is not directly backed up by the battery backup as with the MARK 5/8/9. With the Battery Backup Option and Extended Memory, the MARK 12 will transfer the contents of the onboard memory to and from the Extended Memory during powerfail and restart.

#### 2.3 DATA CHANNEL

The high-speed/standard-speed data channel jumper is no longer required. The MARK 12 has a single, high-speed data channel; all standard controllers should work with the MARK 12.

#### 2.4 DEVICE CODES 2 AND 3

The controls for Device Codes 2 and 3 do not come out on the backplane. They are reserved by the MARK 12 for internal purposes.

#### **2.5 EXTENDED INSTRUCTION SET**

The Extended Instruction Set is not available on the MARK 12.

#### **2.6 BACKPLANE**

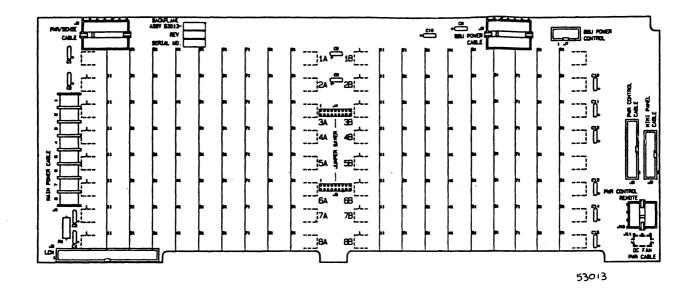

The MARK 12 features a new backplane with improved power distribution. Improved cooling is accomplished through .7-inch spacing and improved air flow.

Slots 2 through 5 are zoned for extended memory but may be used by most devices. The extended memory bus uses backplane pins defined for memory use only.

#### CAUTION

Do not install non-POINT 4 controllers, which may use the pins defined for memory use, in slots 1 through 5. Non-POINT 4 controllers can be installed in any other slot.

The Extended Memory Bus uses the following pins of slots 1-5 for access to extended memory:

| 8A   |      |      | B-5  |

|------|------|------|------|

| A-13 | thru | A-32 | B-9  |

| A-35 | thru | A-37 | B-12 |

| A-39 |      |      | B-14 |

| A-41 |      |      | B-18 |

| A-43 |      |      | B-26 |

| A-45 |      |      | B-28 |

| A-51 |      |      | B-30 |

| A-53 |      |      | B-32 |

| A-55 |      |      |      |

MARK 12 Computer System, Rev 6/86

#### **III. DESCRIPTION OF CPU DIFFERENCES**

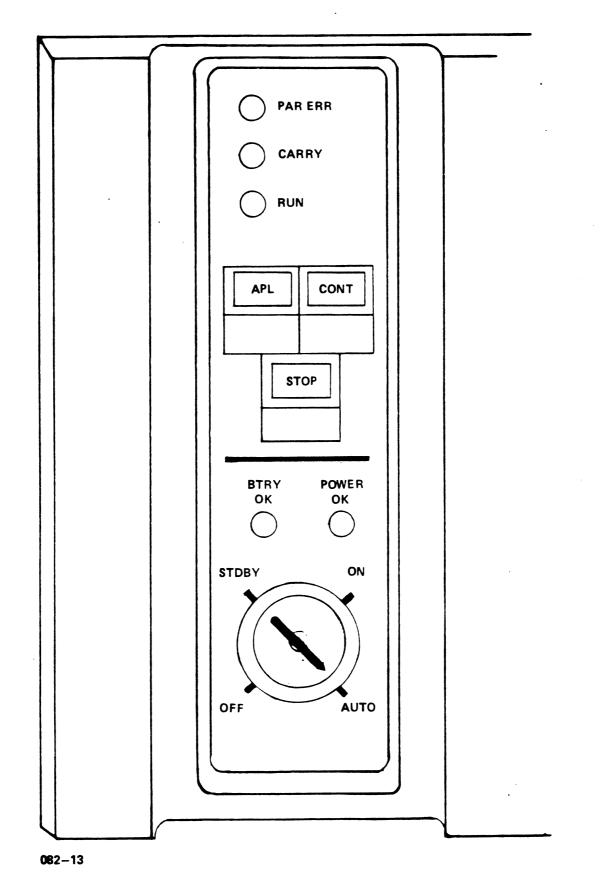

#### 3.1 CPU STATUS LEDS

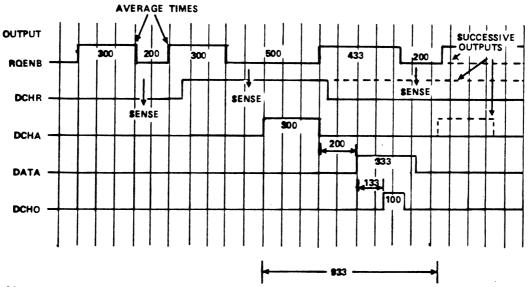

Sixteen small green LEDs at the front edge of the CPU board show the status of the CPU. From the left, they are:

ION - Interrupts are enabled

DME - Data Channel mapping enabled

EIS - CPU is in Extended Instruction Set mode

64K - CPU is in 64K-word addressing mode

DCR - Data Channel Request is active

11-Bit Firmware Microprogram Address

#### **3.2** SELF-TESTING CAPABILITIES

There are two types of self-test on the MARK 12: one firmware (hardware verify), the other software (Self-Test). Both are provided in onboard ROM.

#### <u>Hardware-Verify</u>

The hardware-verify tests the full functionality of the hardware at the firmware level and ensures that the hardware is functional enough to communicate with a terminal. The CPU status LEDs give information regarding errors.

This hardware-verify capability enables the technician to obtain information about the CPU and to debug it when MANIP cannot be loaded because of a hardware problem.

An Operator Control Unit is not required for the MARK 12. Instead, this hardware-verify capability allows examining the program counter, accumulators, CPU status word and 8 words of memory when the CPU is in a Halt state. By pressing any key (except <ESCAPE> which transfers control to MANIP), the following information is displayed on the master terminal:

where

| pppppp | - | value  | of   | progra | m cou | nter  | when   | Halt   | was e | encount | ere | d    |

|--------|---|--------|------|--------|-------|-------|--------|--------|-------|---------|-----|------|

| aaaaaa | - | value  | of   | accumu | lator | 0     |        |        |       |         |     |      |

| bbbbbb | - | value  | of   | accumu | lator | 1     |        |        |       |         |     |      |

| ccccc  | - | value  | of   | accumu | lator | 2     |        |        |       |         |     |      |

| dddddd |   | value  | of   | accumu | lator | 3     |        |        |       |         |     |      |

| SSSSSS | - | saved  | I C  | PU st  | atus  | wor   | :d (   | see    | Appe  | ndix    | Α   | for  |

|        |   | descri | pti  | on)    |       |       |        |        |       |         |     |      |

| vvvvvv |   | value  | in   | mini-s | witch | es or | n from | nt edg | ge of | CPU     |     |      |

| WWWWW  | - | conte  | nt   | of 8 w | ords  | of c  | nboa   | rd me  | mory  | start   | ing | j at |

|        |   | addres | ss v | vvvvv  |       |       |        |        | _     |         | -   | -    |

By manipulating the mini-switches, the user can read any location in onboard memory.

#### Software Self-Test

The software Self-Test is contained in the MANIP PROM; it can be accessed in three ways:

- 1. On power-on

- 2. Using the MANIP T command

- 3. By setting mini-switches located on front edge of CPU to 100200 and pressing APL switch

## Power-On Sequence

On power-on, one pass of the hardware-verify function followed by four passes of the software Self-Test are performed automatically. Control then depends on the setting of the mini-switches:

- if 100200, will run Self-Test forever

- if 200 + x where x is a device code, will IPL from device x

- if other than above, control goes to MANIP

#### 3.3 MANIP - VIRTUAL CONTROL PANEL

The MARK 12 CPU has an expanded MANIP capability. When the APL switch is depressed, a conventional MANIP is loaded into the top 1000 (octal) words of onboard memory. This MANIP in turn gives the capability of loading the remainder of the APL PROMs, or any portion thereof, to any desired location in onboard memory.

There are no separate Self-Test PROMs; instead the expanded MANIP contains Self-Test, and provides for a means of entering it.

The MARK 12 MANIP has all the MARK 5 features plus the following:

- A Displays program counter, 4 accumulators, and CPU status word (see Appendix A for description)

- C Allows modification of CPU status word, e.g.

C4,ssssss

where ssssss is the new CPU status word

- J(without parameter) Does a CONTinue function; i.e., jumps to address where last Halt occurred

- P Initializes extended memory (if any), before performing program load function

- T Loads Self-Test and begins executing it forever (must press CONTinue after initial Halt)

- U Can be used to unload DBUG from PROM into memory, e.g.

U1000,2000,3000

unloads PROM beginning at 1000, for 2000 words into onboard memory starting at location 3000

U(without parameters) - unloads DBUG and BZUD beginning at location 73000

The MARK 12 MANIP also has a signature or prompt; every line starts with

->

It differs from the DBUG signature which is

=>

#### IV. LCM/EXTENDED MEMORY DIFFERENCES

#### 4.1 LCM

The new version of the LCM is fully system and software compatible with the old LCM; it has the following additional features:

- Larger capacity 2 and 4MB

- Additional diagnostic features

- Receives +5V BBU power from the backplane; no need for additional power supply or cabling when used in the MARK 12 chassis with the MARK 12 power supply (the LCM can still be powered in the old way if used in a non-MARK 12 chassis)

#### 4.2 EXTENDED MEMORY

The new MARK 12 Extended Memory is not compatible with the old LCM system. It can be used only with a MARK 12 CPU in a MARK 12 chassis. No extra cabling is required for battery backup; it receives +5 BBU power from the backplane. It is offered in 2 and 4MB boards.

#### MARK 12 Computer System, Rev 6/86

# Appendix A

# CPU STATUS WORD

| Bit   | Symbol       | Name and Significance                                                                                                                                                                                                                     |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0*    | СҮ           | Carry flag in saved CPU status word. Always 0 in<br>current status. If set by software to a 1, along<br>with MSK=0, will set 64KW-addressing mode and<br>enable EIS (if implemented), ignoring all other<br>bits in the NIOP instruction. |

| 1     | MSK          | Mask. If set to a 0 by software in a NIOP, bits<br>2-14 will be ignored. If set to a 1, enable bits<br>2-14. Always set to 1 during a read.                                                                                               |

| 2     | AUT          | Auto Restart flag. Set by hardware to a 1, in<br>saved CPU status word, on power up, if front panel<br>keyswitch is in the AUTO position. General<br>purpose flag otherwise.                                                              |

| 3     |              | Reserved.                                                                                                                                                                                                                                 |

| 4     |              | Reserved.                                                                                                                                                                                                                                 |

| 5     |              | Reserved.                                                                                                                                                                                                                                 |

| 6     |              | Reserved.                                                                                                                                                                                                                                 |

| 7     | TSC          | Trap Self-modifying Code control bit. Set by software to a 1 to enable.                                                                                                                                                                   |

| 8     | PEL          | Front panel Parity Error Light control bit. Set<br>to a 1/0 by software to turn parity error light<br>on/off.                                                                                                                             |

| 9     | Ml2          | MARK 12 mode control bit. If set by software to a 1, along with 64K=1, will enable MARK 12 mode.                                                                                                                                          |

| 10    | -            | Reserved.                                                                                                                                                                                                                                 |

| 11    | RNL          | Run flag. Set to a 1/0 by hardware to indicate<br>Run/Halt state. Also set by hardware to a 0, in<br>saved CPU status word, at power up.                                                                                                  |

| 12    | ION          | Interrupts Enabled flag. Set by hardware only to indicate interrupts enabled.                                                                                                                                                             |

| 13    | DME          | Data channel Map Enable flag. Set by software to a 1 to enable data channel mapping.                                                                                                                                                      |

| 14    | -            | Reserved for EIS enablement.                                                                                                                                                                                                              |

| 15    | 6 <b>4</b> K | 64KW-addressing mode control bit. Must set to a l to enable M12 mode or TSC control bit.                                                                                                                                                  |

| *Most | significa    | nt bit                                                                                                                                                                                                                                    |

--Antonia **4**49999-5-17

# Chapter 2 - FUNCTIONAL DESCRIPTION

## CONTENTS

# Paragraph

## Title

|     | Genera  |                                                                        | 2B-2           |

|-----|---------|------------------------------------------------------------------------|----------------|

| 2.2 | MARK 1  | 2 CPU Signals                                                          | 2B-2           |

|     | 2.2.1   |                                                                        | 2B-2           |

|     |         | 2.2.1.1 System Clock (SYSCLK-)                                         | 2B-3           |

|     |         | 2.2.1.2 Data/Address Lines (V0-/V31-)                                  | 2B-3           |

|     |         | 2.2.1.3 Address Strobe (AS-)                                           | 2B-3           |

|     |         | 2.2.1.4 Data Strobe (DS-)                                              | 2B-3           |

|     |         | 2.2.1.5 Write Data (WRITE-)                                            | 2B-3           |

|     |         | 2.2.1.6 Long Word (LWORD-)                                             | 2B-4           |

|     |         | 2.2.1.7 Bus Busy (BBSY-)                                               | 2B-4           |

|     |         | 2.2.1.8 Data Transfer Acknowledge (DTACK-)                             | 2B-4           |

|     |         | 2.2.1.9 Bus Error (BERR-)                                              | 2B <b>-4</b>   |

|     |         | 2.2.1.10 Bus Error Correction Attempt                                  |                |

|     |         | (BERC-)                                                                | 2B-4           |

|     | 2.2.2   | Power Fail/Power Gone Signals                                          | 2B-5           |

|     |         | 2.2.2.1 Power Fail (PWRF-)                                             | 2B-5           |

|     |         | 2.2.2.2 Power Gone (PWRGON-)                                           | 2B-5           |

| 2.3 | Program |                                                                        | 2B-5           |

|     |         | Overview                                                               | 2B-5           |

|     | 2.3.2   | Software Modes                                                         | 2B-5           |

|     |         | 2.3.2.1 32K Word Addressing Mode                                       | 2B-6           |

|     |         | 2.3.2.1.1 Indirect Addressing                                          | 2B-6           |

|     |         | 2.3.2.1.2 Auto Indexing                                                | 2B-6           |

|     |         | 2.3.2.1.3 Self-Modifying Code                                          | 2B-7           |

|     |         | 2.3.2.2 64K Word Addressing Mode                                       | 2B-7           |

|     |         | 2.3.2.3 Extended Instruction Set (EIS)                                 |                |

|     |         | Mode                                                                   | 2B-8           |

|     |         | CPU Status Word                                                        | 2B-9           |

|     | 2.3.5   |                                                                        | 2B-12          |

|     |         | 2.3.5.1 Read Hardware/Firmware                                         |                |

|     |         | Identification, Status Word, Etc.                                      |                |

|     |         | 2.3.5.2 Load Program from APL Prom                                     | 2B-13          |

|     |         | 2.3.5.3 Expansion Memory Access                                        | 2B-13          |

|     |         | 2.3.5.3.1 CPU Access to Expansion                                      | 20.12          |

|     |         | Memory<br>2.3.5.3.1.1 Multiple Word Transfers                          | 2B-13<br>2B-14 |

|     |         | 2.3.5.3.1.2 Block Transfers                                            | 2B-14<br>2B-15 |

|     |         |                                                                        | 2B-15<br>2B-16 |

|     |         | 2.3.5.3.1.3 Single Word Transfers<br>2.3.5.3.1.4 Single Word Transfers | 20-10          |

|     |         | With Data Channel MAP                                                  |                |

|     |         | Translation                                                            | 2B-17          |

|     |         | 2.3.5.3.2 Data Channel Access To                                       | 20-11          |

|     |         |                                                                        |                |

|     |         | Expansion Memory - Data<br>Chappel Map                                 | 20-20          |

|     | 2 2 C   | Channel Map<br>Power On Initialization                                 | 2B-20<br>2B-22 |

|     | 2.3.6   | FOWEL OIL THILLIALIZACION                                              | 40-44          |

|     |         |                                                                        |                |

#### CHAPTER 2

#### FUNCTIONAL DESCRIPTION

#### 2.1 GENERAL

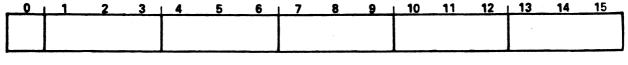

The MARK 12 is a 16-bit Data General Nova\*compatible CPU with 128K bytes of onboard static ram. In addition, the MARK 12 can access up to 16 megabytes of external memory located on MARK 12 memory expansion boards, each containing from 2 to 4 megabytes. The CPU uses a pipelined architecture, with a four instruction prefetch queue, and an autonomous Data Channel processor.

The MARK 12 CPU is an extension of that part of POINT 4 Data Corporation's product line that consists of the MARK 5, MARK 8, and MARK 9 computers. It uses the same size printed circuit board, and is compatible with the same peripheral controllers.

2.2 MARK 12 CPU SIGNALS

Signals common to the Data General Nova are defined in the Nova User's Manual (see list of reference documents). Signals unique to the CPU are described below. All are low-active signals, indicated by the "-" suffix.

#### 2.2.1 32-BIT HIGH SPEED BUS TO EXPANSION MEMORY

The MARK 12 CPU features a 32-bit high speed synchronous extension memory bus used to access expansion memory boards in the MARK 12 system. Data is transferred on this "V-Bus" along 32 parallel, bidirectional, data lines. Control and status signals are carried along dedicated, unidirectional, control and status lines. This structure uses 41 pins on the 200-pin Nova backplane. The pins used are all taken from the set of pins reserved by the standard Data General Nova pinout for memory lines, that is, pins which are not permitted to be used by custom interface boards.

The 41 pins are defined as follows:

(from MARK 12 CPU Product Specification)

2B-2

#### 2.2.1.1 SYSTEM CLOCK (SYSCLK-)

A 12.5 MHz (nominal) signal from the CPU used to synchronize the optional expansion memory to the CPU, and to synchronize the transfer of data. The memory uses only the low-going edge of this signal.

2.2.1.2 DATA/ADDRESS LINES (V0-/V31-)

32 bi-directional lines used to transfer both addresses (from CPU, strobed by AS-) and data (from CPU, strobed by DS-, or from expansion memory, strobed by DTACK-). V0 is the most significant bit (MSB).

2.2.1.3 ADDRESS STROBE (AS-)

This signal is generated by the CPU when a new expansion memory block address is on the V1-/V15lines. A single address strobe may be followed by a sequence of data strobes.

2.2.1.4 DATA STROBE (DS-)

This signal is generated by the CPU to indicate that valid data is present on the VO-/V31- lines during an expansion memory write cycle, or that more data is requested during a read cycle. Each data strobe causes two successive 32-bit transfers for a 64-bit quadruple word transfer; and up to 64 such pairs, separated by at least one idle state (80 nanoseconds), may be used to transfer up to a 256-word page to or from memory.

Note: When both AS- and DS- are activated at the same time, the meanings of VO- and V8-/V15- are as follows:

The V8-/V15- lines hold a word address offset into the memory page addressed by the AS-only transfer. This is used for single-word transfers (DMA) and for partial page transfers (less than 256 words).

The VO- line, if active, indicates that the EDAC logic on the expansion memory is to be bypassed, for diagnostic purposes only.

2.2.1.5 WRITE DATA (WRITE-)

A control signal generated by the CPU and indicating that data is to be written to expansion memory. When this signal is inactive (high), data is to be read from memory.

(from MARK 12 CPU Product Specification)

2B-3

2.2.1.6 LONG WORD (LWORD-)

A signal generated by the CPU indicating that the current transfer is a part of a multi-word transfer, transferring 32 bits at a time. When this signal is inactive (high), and WRITE- is active, it means to write one word only to the specified word address. If WRITE- is inactive, it means to read the expansion memory status word onto the V0-/V15- lines (refer to Section 2.3.5.3.1).

2.2.1.7 BUS BUSY (BBSY-)

This signal is an open-collector signal generated by the expansion memory in response to the ASsignal if the memory contains the block address on the V1-/V15- lines.

2.2.1.8 DATA TRANSFER ACKNOWLEDGE (DTACK-)

Data Transfer Acknowledge; an open-collector signal generated by the memory to indicate that valid data is available on the bus during a read cycle, or that data has been accepted from the bus during a write cycle.

2.2.1.9 BUS ERROR (BERR-)

An open-collector signal generated by expansion memory to indicate that the data read from memory contains an error, either correctable or not, and that correction will be automatically attempted.

**2.2.1.10** BUS ERROR CORRECTION ATTEMPT (BERC-)

An open-collector signal generated by the expansion memory to indicate that a data correction attempt is being made.

BERR- BERC-

| н | Н            | No error                            |    |

|---|--------------|-------------------------------------|----|

| L | Н            | Some error, correction will be      |    |

|   |              | attempted                           |    |

| H | $\mathbf{L}$ | Correction was successful           |    |

| L | $\mathbf{L}$ | Correction attempt was unsuccessful | L; |

|   |              | i.e., a multi-bit error occurred    |    |

2B-4

#### 2.2.2 POWER FAIL/POWER GONE SIGNALS

These two signals must be generated by the power supply providing power to the MARK 12 CPU.

2.2.2.1 POWER FAIL (PWRF-)

The Power Fail signal is an early warning indication to the MARK 12 CPU of impending power failure. This signal must occur at least 5 milliseconds before DC power goes out of regulation.

When PWRF- goes active, a non-maskable program interrupt is generated which allows the software to gracefully shut down the entire system. If the system in which the CPU is installed also contains MARK 12 memory boards with battery backup, this shutdown would also include copying the contents of CPU memory to expansion memory.

2.2.2.2 POWER GONE (PWRGON-)

PWRGON- is asserted by the CPU chassis power supply to indicate to the MARK 12 CPU that DC power is now out of regulation. When received by the CPU, this signal will result in a CPU hardware reset. PWRGON- must be asserted for 1 microsecond minimum, or as long as power remains out of regulation. When power is restored, after a power failure or brownout, PWRGON- must remain asserted until DC power is within regulation.

- 2.3 PROGRAMING

- 2.3.1 OVERVIEW

The MARK 12 CPU software interface is generally compatible with the basic instruction set of the POINT 4 MARK 5 CPU, in both 32K Word and 64K Word addressing modes. The remainder of this section documents the differences from those standards.

2.3.2 SOFTWARE MODES

The MARK 12 CPU has a number of operational modes, which are controlled by a set of mode bits. The use of mode bits, combined in a 16-bit CPU Status Word, makes for a very powerful and structured way of setting, saving, restoring, and displaying the CPU's operating mode.

(from MARK 12 CPU Product Specification)

#### 2.3.2.1

#### 32K WORD ADDRESSING MODE

The 32K Word addressing mode is available in the MARK 12 CPU to allow the user to emulate the original Data General Nova CPUs that had only 64KB of available memory. Indirect addressing chains (see below) and auto-increment/decrement locations (see Section 2.3.2.1.2) are functional in this mode. Data Channel Mapping (see Section 2.3.5.3.2) may be enabled as necessary and unrestricted "self-modifying code" (refer to Section 2.3.2.1.3) is also allowed. In 32K mode there is an attendant performance loss due to the additional overhead of 32K mode emulation.

After an IORST instruction is executed, the CPU is automatically placed in 32KW mode, with Data Channel Mapping disabled. 32KW mode can also be entered (with Data Channel Mapping unaffected) by executing an NIOP CPU instruction with 0 in A0; see Section 2.3.4 below.

**2.3.2.1.1** INDIRECT ADDRESSING

With the MARK 12 CPU in 32KW mode, all memory references are limited to 15 bits of address, with the most significant bit ignored in direct addressing and used for multi-level indirection in indirect addressing. The MARK 12 CPU provides no protection against infinite indirection.

2.3.2.1.2

#### AUTO INDEXING

If an indirect address points to a location in onboard memory in the range 20-27 (octal), that word is fetched, the contents of the word is incremented by one and written back into the This updated value is then used to location. continue the addressing chain. The locations 20-27 are referred to as the auto-increment locations. If an indirect address points to a location in the range 30-37 (auto-decrement locations), that word is fetched, the contents of the word is decremented by one and written back into the location. The updated value is then used to continue the addressing chain. The POINT 4 IRIS Operating System does not use this capability; the MARK 2/3/4 series of CPUs do not implement it.

In the MARK 12 CPU, auto-increment/decrement locations are implemented only when in 32KW or 64KW mode. In MARK 12 mode there is no Auto Indexing.

(from MARK 12 CPU Product Specification)

### 2.3.2.1.3 SELF-MODIFYING CODE

Since the MARK 12 CPU uses an instruction prefetch scheme, there is a potential problem if the software program being executed attempts to modify an instruction which is imminently to be executed. If the instruction is already in the Instruction Prefetch Queue (see Section 3.3), the modified instruction will be stored into onboard memory, but the unmodified instruction will be executed.

Of course the CPU hardware/firmware could always test for this condition in all Store and ISZ/DSZ instructions, but the performance penalty would be noticeable.

The problem is resolved in the MARK 12 CPU by allowing unrestricted self-modifying code when the CPU is running in either 32K or 64K (see Section 2.3.2.2) mode, since neither of these modes are considered as the preferred operational mode.

In normal MARK 12 mode, it is illegal to modify an instruction and then flow into it, ie., proceed to execute the modified instruction without an intervening JMP or JSR (any Jump instruction reloads the Instruction Prefetch Queue).

#### **2.3.2.2 64**K WORD ADDRESSING MODE

In this mode, all 16 bits are used as a word address, allowing access to 64K Words, or 128K Bytes of onboard memory. As a result, multi-level indirect addressing is not available in this mode. However, auto-increment/decrement locations are functional and self-modifying code is also allowed. Data Channel Mapping may be enabled or disabled as desired.

As an aid to systems software developers, there is an additional feature available to the user which is not available in either of the other two operational modes. That is, the ability to force the CPU to generate a software trap when instruction sequences are encountered which are not allowed while in the MARK 12 mode of operation; namely, self-modifying code and code which utilizes any of the sixteen auto-increment/ decrement registers. By setting/clearing the TRP bit in the CPU Status Word (see Section 2.3.4), this diagnostic function can be enabled or disabled. With the TRP bit set, a software trap will be executed whenever a STA, ISZ or DSZ instruction has an effective address which is 1-5 words in front of itself, or if a STA or LDA instruction addresses any of the sixteen auto-increment/ decrement registers. The trap is executed as follows: The two words preceding the program interrupt service routine, to which there is a pointer contained in onboard memory at location 1, are used. The contents of the updated program counter at the time the trap occurred is stored in the first of these, and the second is used as a vector to the trap handler. It is then up to the trap handler to determine if there is an intervening JMP or JSR or if the self-modifying code restriction is violated, and to take any appropriate action.

#### 2.3.2.3 EXTENDED INSTRUCTION SET (EIS) MODE

In EIS mode the class of ALU instructions having both the No-Load bit set and the Unconditional-Skip code set, is redefined as a set of macroinstructions implementing such functions as:

Binary Multiply and Divide

Decimal (BCD) Add and Subtract

Byte Access: GETBYTE and PUTBYTE

Immediate Compare, Load, Add and Subtract

Bit Test and Modify instructions

Block Move

Table Search

Stack instructions

In the MARK 12, the EIS mode is disabled. However, the hardware exists to implement it at a later date.

2B-8

The MARK 12 CPU Status Word is defined as shown in table 2-1. CPU Status can be set by an NIOP CPU instruction; it is read by a DIAP ac,CPU instruction with (ac) = 2 (see Section 2.3.5.1). Further, the MARK 12 hardware saves the current CPU status in an auxiliary register ("saved status") whenever the HALT state is entered. Saved status is read by a DIAP ac,CPU instruction with (ac) = 1. Refer to Section 2.3.6 for the default condition of the status word at power up time. Bit 0 is the MSB.

### TABLE 2-1 CPU STATUS WORD

| Bit  | Symbol   | Name and Significance                                                                                                                                                                                                               |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | СХ       | Carry flag in saved CPU status word.<br>Always 0 in current status. If set<br>by software to a 1, along with MSK =<br>0, will set 64K mode and enable EIS<br>(if implemented), ignoring all other<br>bits in the NIOP instruction.* |

| 1    | MSK      | Mask. If set to a 0 by software in<br>a NIOP, bits 2-14 will be ignored.<br>If set to a 1, enable bits 2-14.<br>Always set to 1 during a read.                                                                                      |

| 2    | AUT      | Auto Restart flag. Set by hardware<br>to a 1, in saved CPU status word, on<br>power up, if front panel keyswitch<br>is in the AUTO position. General<br>purpose flag otherwise.                                                     |

| 3    | -        | Reserved.                                                                                                                                                                                                                           |

| 4    | -        | Reserved.                                                                                                                                                                                                                           |

| 5    | -        | Reserved.                                                                                                                                                                                                                           |

| 6    | -        | Reserved.                                                                                                                                                                                                                           |

| 7    | TSC      | Trap Self-Modifying Code control<br>bit. Set by software to a 1 to<br>enable. See section 2.3.2.4 for<br>detailed explanation.                                                                                                      |

| 8    | PEL      | Front panel parity error light<br>control bit. Set to a 1/0 by<br>software to turn parity error light<br>on/off.                                                                                                                    |

| 9    | M12      | MARK 12 Mode control bit. If set by software to a 1, along with 64K=1, will enable MARK 12 Mode.                                                                                                                                    |

| 10   | -        | Reserved.                                                                                                                                                                                                                           |

| *See | Notes on | page 2B-12.                                                                                                                                                                                                                         |

2B-10

### TABLE 2-1 CPU STATUS WORD (CONT.)

| Bit | Symbol | Name and Significance                                                                                                                       |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | RNL    | Run flag. Set to a 1/0 by hardware<br>to indicate Run/Halt state. Also<br>set by hardware to a 0, in saved CPU<br>status word, at power up. |

| 12  | ION    | Interrupts Enabled Flag. Set by<br>hardware only to indicate interrupts<br>enabled.                                                         |

| 13  | DME    | Data Channel Map Enable Flag. Set<br>by software to a l to enable Data<br>Channel mapping.                                                  |

| 14  | -      | Reserved for EIS enable bit.                                                                                                                |

| 15  | 64K    | 64K Addressing mode control bit.<br>Must set to a l to enable Ml2 or<br>TSC control bit.                                                    |

•

1

.....

Note: Bits 0 and 1 in the NIOP case are defined so as to allow compatibility with existing code, since the MARK 5/8/9 CPUs have used the NIOP with the following values:

000001 = Set 64K mode 100001 = Set EIS and 64K mode 177777 = Set EIS and 64K mode 000000 = Set 32K mode, no EIS

Bits 0 and 1 in the DIAP case are defined so that they do not need to be changed for a subsequent NIOP instruction in the new format.

Note: To set the CPU Status Word, the customary way is to use an NIOP CPU instruction, with the appropriate value in accumulator 0. Alternatively, a different accumulator may be used, although the assembler will then not accept the NIOP mnemonic.

2.3.5 SPECIAL CPU ACCESS INSTRUCTIONS

2.3.5.1

READ HARDWARE/FIRMWARE IDENTIFICATION, STATUS WORD, ETC.

In the standard MARK 5 CPU instruction set, a DIA ac, 77 instruction reads the 16 mini-switches on the front edge of the CPU board into the specified accumulator. If the DIA instruction is accompanied by a Start or Clear pulse, it will simultaneously enable or disable interrupts. The Pulse signal does not have any effect in I/O instructions to device 77 (CPU).

In the MARK 12 CPU, all the above works exactly the same, except that the DIAP instruction has a new definition:

DIAP ac,77

returns a value in the specified accumulator which depends on the original content of that accumulator.

| Entry | Value Returned                                      |

|-------|-----------------------------------------------------|

| 0     | Hardware/Firmware Identification                    |

| 1     | CPU Status Byte saved when HALT state<br>is entered |

| 2     | Current CPU Status Byte                             |

| >2    | Same as O                                           |

The Hardware/Firmware Identification word is defined as follows:

Left byte = Hardware ID = 12 (octal), defines MARK 12 CPU Right byte = Firmware ID = 1 for initial release The CPU Status Word is defined in Section 2.3.4.

2.3.5.2 LOAD PROGRAM FROM APL PROM

The NIO CPU instruction is used to read in any program contained in the APL PROM on the CPU board and to begin executing it.

- A0 = Address in the APL PROMs from which the program will be loaded

- Al = Number of words to be loaded

- A3 = Starting address in onboard memory to begin program execution

- All accumulators are preserved.

- 2.3.5.3 EXPANSION MEMORY ACCESS

- 2.3.5.3.1 CPU ACCESS TO EXPANSION MEMORY

The MARK 12 CPU uses four pairs of I/O instructions to access expansion memory; one for multiple word transfers to or from onboard memory, one for single "block" transfers to or from onboard memory, and two for single word transfers to or from accumulator 2. One of the two pairs of I/O instructions used to transfer single words also allows Data Channel Map translation. However, all other expansion memory access instructions have no map translation. In all of the following descriptions, the mnemonic "MEM" represents the device code, which is 2 for expansion memory access.

(from MARK 12 CPU Product Specification)

### 2.3.5.3.1.1 MULTIPLE WORD TRANSFERS

DIA and DOA are used to transfer multiple words between expansion memory and onboard memory. The specifics are detailed as follows:

DIA ac, MEM Read from expansion memory to onboard memory.

DOA ac, MEM Write from onboard memory to expansion memory.

In both of the instructions above, all four accumulators have prescribed meanings, regardless of which accumulator is coded in the instruction. They are,

A0 = Number of words to transfer (maximum 400 octal). This value must be a multiple of 4; i.e., the two least significant bits are ignored. If (A0) = 0, no transfer is done.

Al = Block number in expansion memory, where a block is defined as 256 words. The block number may range up to 77777 (octal) for 16 MB addressing.

A2 = Onboard address; i.e., address in onboard memory from which data is to be transferred. Must be a multiple of 4; i.e., the two least significant bits are ignored and taken as 00.

A3 = Bits 8-15: Word address offset into the block in expansion memory addressed by A1, where the transfer is to begin. Must be a multiple of 4; i.e., the two least significant bits are ignored and taken as 00.

Bit 0: If the msb of A3 is 1, the Error Detection and Correction circuitry is disabled. On a read, the data is read regardless of any error indication and no attempt at error correction is made. On a write, only the new data is written to the addressed quadruple-word in expansion memory, preserving the previously existing Error Correction bits.

Note: Transfer may not overlap from one block into the next. In other words, the sum (A0) + (A3) must not exceed 400 octal.

(from MARK 12 CPU Product Specification)

#### 2.3.5.3.1.2 BLOCK TRANSFERS

DIB and DOB are used to transfer entire blocks (256 words) between expansion memory and onboard memory. The specifics are detailed as follows:

DIB ac, MEM Read a block from expansion memory to onboard memory.

DOB ac, MEM Write a block from onboard memory to expansion memory.

In both the above, Al and A2 have prescribed meanings, regardless of which accumulator is coded in the instruction.

Al = Block number in expansion memory

A2 = Onboard memory address

Note: Error Detection and Correction cannot be disabled as with the DOA/DIA instructions.

In all four of the above instructions, after execution the accumulators will be as follows:

A0 = Expansion memory status word (see Table 2-2)

Al = Unchanged

A2 = Next onboard memory address, i.e., A2 is incremented by the number of words transferred

A3 = Unchanged

### 2.3.5.3.1.3 SINGLE WORD TRANSFERS

1

DIC and DOC are used to transfer single words between expansion memory and accumulator 2. The specifics are detailed as follows:

DIC ac, MEM Read one word from expansion memory into accumulator 2.

DOC ac, MEM Write one word from accumulator 2 into expansion memory.

In both of the instructions above, Al and A3 have prescribed meanings, regardless of which accumulator is coded in the instruction. They are,

Al = Block number containing the desired word in expansion memory

A3 = Bits 8-15: Word address offset of the desired word into the block in expansion memory addressed by A1.

Note: Error Detection and Correction cannot be disabled as with the DOA/DIA instructions.

In both of the above instructions, after execution the accumulators will be as follows:

A0 = Expansion memory status word (see Table 2-2)

Note: The status word returned is 0 if there are no error conditions to report; i.e., if the lsb = 0 then the entire status word is equal to zero.

Al = Unchanged

A2 = The word read from expansion memory when using DIC; unchanged when using DOC.

A3 = Unchanged

2.3.5.3.1.4 SINGLE WORD TRANSFERS WITH DATA CHANNEL MAP TRANSLATION

DIC/DOC ac,MAP are used to transfer single words between expansion memory and accumulator 2 using the Data Channel Map address translation features (refer to 2.3.5.3.2). The specifics are detailed as follows:

DIC ac,MAP Read one word from expansion memory into accumulator 2 with address translation. The mnemonic "MAP" represents the device code, which is 3 for Data Channel Map access.

DOC ac, MAP Write one word from accumulator 2 into expansion memory with address translation.

In both of the instructions above, A3 has a prescribed meaning, regardless of which accumulator is coded in the instruction. It is,

A3 = Logical address of the desired word in onboard or expansion memory, depending on the contents of the Data Channel Map.

Note: Error Detection and Correction cannot be disabled as with the DOA/DIA instructions.

After execution, the accumulators will be as follows:

A0 = Expansion memory status word (see Table 2-2), or 0 if word referenced is located in onboard memory, or if there are no error conditions to report.

Al = Block address as read from Data Channel Map (refer to Section 2.3.5.3.2).

A2 = The word read from expansion memory when using DIC; unchanged when using DOC.

A3 = Unchanged

### TABLE 2-2 EXPANSION MEMORY STATUS WORD

| Bit  | Symbol | Name and Significance                                                                                                                                                                                                                                                                              |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    |        | Reserved.                                                                                                                                                                                                                                                                                          |

| 1    | DON    | Done Flag. Set by hardware to a 1<br>to indicate that the previous<br>transfer was accomplished. A 0<br>indicates that no memory board with<br>the specified block number has<br>responded. In this case, ERR is<br>also set to a 1.                                                               |

| 2    | EDC    | Error Detection and Correction<br>(EDAC) Option Flag. Set by<br>hardware to a 0 if the EDAC option<br>is installed.                                                                                                                                                                                |

| 3-10 | C0/C7  | These are the 8 EDAC check bits<br>written or read along with the 64<br>data bits. Used for diagnostic<br>purposes only.                                                                                                                                                                           |

| 11   | VIR    | Virgin Flag. This bit is set to a<br>l by a DOA, DOB or DOC instruction<br>(i.e., a write to expansion memory),<br>and cleared by hardware at<br>expansion memory power-up time. At<br>Power-Fail Auto-Restart time, if<br>this bit is 0, it indicates that<br>Battery Back-up was not successful. |

| 12   | BAK    | Battery Back-up Option Flag. Set<br>by hardware to a l if the expansion<br>memory BBU option is installed.                                                                                                                                                                                         |

| 13   | SER    | System Error Flag. Set by hardware<br>to a 1 to indicate that an error<br>has occurred on a mapped data<br>channel input (to write 1 word, the<br>expansion memory must first read 4<br>words). Cleared by any instruction<br>that reads the expansion memory<br>status.                           |

| 14   | CER    | Correctable Error Flag. Set by<br>hardware to indicates that a<br>correctable error has occurred on<br>the last transfer; the error was<br>corrected both in onboard memory<br>and in expansion memory. Cleared<br>by an instruction that reads the<br>expansion memory status.                    |

## TABLE 2-2 EXPANSION MEMORY STATUS WORD (CONT.)

| Bit<br> | Symbol | Name and Significance                                                                                                                                                                                                                                      |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | ERR    | Error Flag. Set by hardware to a 1<br>to indicate that there has been<br>an error on the last transfer. If<br>Bit 14 is 0, it indicates that the<br>error was uncorrectable. Cleared<br>by any instruction that reads the<br>expansion memory status read. |

(from MARK 12 CPU Product Specification)

2B-19

If it is desired to read the expansion memory status word without doing any memory transfer, this can be accomplished by a DIA ac,MEM instruction with zero in A0.

Any other I/O instructions with device code MEM will have no effect on the expansion memory.

2.3.5.3.2

DATA CHANNEL ACCESS TO EXPANSION MEMORY - DATA CHANNEL MAP

The MARK 12 CPU features a Data Channel Map which allows arbitrary Data Channel access to onboard memory, and block-mapped Data Channel access to expansion memory.

The Data Channel Map is actually a 256 word x 16 bit memory, where each word corresponds to one 256-word block in logical addressing space, and 15 of the 16 bits define the physical "block address" corresponding to that logical block. The 16th bit indicates whether a Data Channel transfer is to go into or out of onboard memory or expansion memory.

On power-up and after an IORST instruction, Data Channel mapping is disabled, i.e., all Data Channel transfers will go into or out of onboard memory without address translation. This is done so that the standard disk bootstrap routine will bring the initial block into onboard memory, where it can be executed.

When a Data Channel request occurs and mapping has been enabled by setting the Data Channel Mapping Enable bit in the CPU Status Word (see Section 2.3.4), the CPU reads the 16-bit address furnished by the requesting device, and applies the 8 most significant bits thereof as an address into the Data Channel Map. If the content of that word in the Data Channel Map has the most significant bit set, the Data Channel transfer is done into or out of onboard memory, otherwise it goes to expansion memory for the transfer. The 15 bits from the Data Channel Map are then combined with the 8 least significant bits of the given 16-bit address to form a 23-bit address, and the Data Channel transfer is done to or from the translated address.

If the software wishes to have Data Channel Mapping enabled, it must first set up the Data Channel Map appropriately, and then set the Data Channel Map Enable mode bit in the CPU Status Word. For each block (256 words) in logical addressing space that is to be mapped into expansion memory, the following instruction must be executed:

DOB ac, MAP

where (regardless of "ac"),

MAP = 3 (device code)

A1 = M\*100000 (octal) + B

where M = 0 for transfers to or from expansion

memory

M = 1 for transfers to or from onboard memory

B = block address (up to 77777 octal for expansion memory or 377 for onboard memory)

A2 = Bits 0-7 = Logical block address given by the Data Channel device, i.e., bits 0-7 of the Data Channel address. Bits 8-15 = Ignored.

For any block that is not to be mapped, or to disable mapping after it has been enabled, use the same instruction to vector the block to itself; i.e., right half of Al = left half of A2.

No warning is given here if expansion memory with the specified block number does not exist on the system. If Data Channel access to non-existent memory is later attempted, input will be discarded, and output will be zero-filled.

To read the content of the Data Channel Map, use a DIB ac,MAP with (A2) as above, and it will return the Map content in Al.

(from MARK 12 CPU Product Specification)

#### POWER ON INITIALIZATION

When power is first applied to the CPU, the firmware goes through the following initialization sequence:

It performs a firmware self-test routine.

It sets all accumulators and the carry bit to zero.

It sets the program counter to zero.

It sets the 64K mode bit and clears the ION, DME, and RNL bits in the CPU status word. It generates an IORST pulse on the I/O bus to initialize all peripheral controllers.

If the key switch on the front panel is in the Auto position, it sets the AUT bit in the CPU status word to 1, otherwise it clears it.

It then loads MANIP (see Section 2.4) into the top 1000 words (octal) of onboard memory and begins to execute it.

From this point on, the MANIP (software) program controls the operation of the CPU. MANIP functions relevant to power-up are as follows: