# POINT 4 MARK III COMPUTER USER MANUAL

# **POINT**/

Ţ.

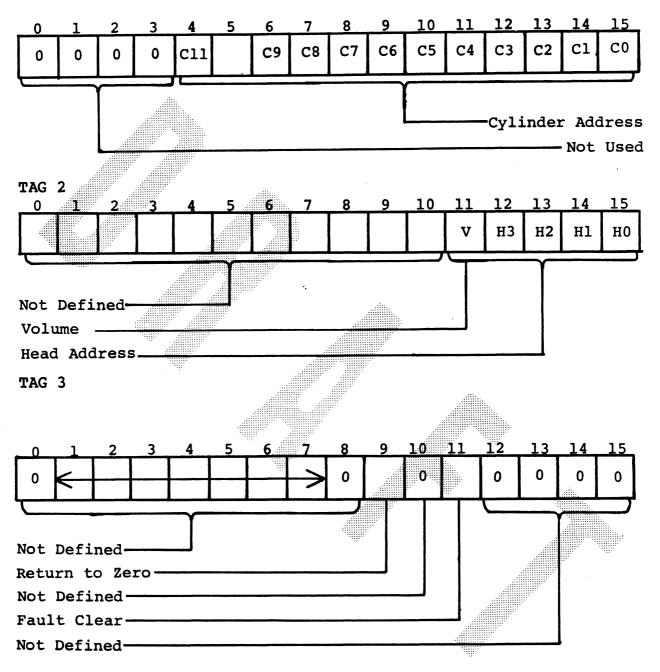

and the second

Sec. Sec.

.

# POINT 4 DATA CORPORATION 2569 McCabe Way, Irvine, California 92714

POINT 4 MARK III COMPUTER

USER MANUAL

| 444       |        |

|-----------|--------|

| 4444      | 44     |

| 444 4     | 4444   |

| 44 444    | 44444  |

| 4 44444   | 444444 |

| 444444    | 444444 |

| 444444444 | 44444  |

| 44444444  | 4444   |

| 444444    | 44     |

| 44444     |        |

DRAFT VERSION

# NOTICE

Every attempt has been made to make this reference manual complete, accurate and up-to-date. However, all information herein is subject to change due to updates. All inquiries concerning this manual should be directed to POINT 4 Data Corporation.

DRAFT

Copyright <sup>(C)</sup> 1981 by POINT 4 Data Corporation (formerly Educational Data Systems, Inc). Printed in the United States of America. All rights reserved. No part of this work covered by the copyrights hereon may be reproduced or copied in any form or by any means--graphic, electronic, or mechanical, including photocopying, recording, taping, or information and retrieval systems--without the written permission of:

> POINT 4 Data Corporation 2569 McCabe Way Irvine, CA 92714 (714) 754-4114

HM-080-0019-01 POINT 4 Data Corporation DRAFT MARK III User Manual

ii

# **REVISION RECORD**

# PUBLICATION NUMBER: HM-080-0019

Date **Description Revision** Draft Version to coincide with delivery of first MARK III 01 05/15/81

HM-080-0019-01 POINT 4 Data Corporation iii

DRAFT MARK III User Manual

### LIST OF EFFECTIVE PAGES

Changes, additions, and deletions to information in this manual are indicated by vertical bars in the margins or by a dot near the page number if the entire page is affected. A vertical bar by the page number indicates pagination rather than content has changed.

| Page                                                                                                                                                                                                                                                                           | Rev                                                                             | Page | Rev | Page | Rev |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|-----|------|-----|

| Cover<br>Title<br>ii thru xiii<br>1-1 thru 1-12<br>2-1 thru 2-6<br>3-1 thru 3-20<br>4-1 thru 4-5<br>5-1 thru 5-35<br>6-1 thru 5-35<br>6-1 thru 6-95<br>Appendix Title<br>A-1 thru A-n<br>B-1 thru B-n<br>C-1 thru C-n<br>D-1 thru D-n<br>Comment Sheet<br>Mailer<br>Back Cover | -<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01 |      |     |      |     |

HM-080-0019-01 POINT 4 Data Corporation

DRAFT MARK III User Manual

iv

PREPACE

CONTENTS

| <u>Section</u>                                                                                                                                                                 | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                                                                              | INTRODUCTION AND GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1                                                                                                             |

| 1.4.1.1<br>1.4.1.2                                                                                                                                                             | Scope<br>General Description<br>Features<br>Equipment Characteristics<br>Performance Characteristics<br>Equipment Specifications<br>System Architecture<br>System Functional Units<br>Central Processor and Memory Board<br>Processor Chassis and Front Panel<br>Processor Mini-Panel<br>Power Supply Board                                                                                                                                                             | 1-1<br>1-3<br>1-4<br>1-4<br>1-5<br>1-6<br>1-8<br>1-9<br>1-11<br>1-11                                            |

| 2                                                                                                                                                                              | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1                                                                                                             |

| 2.1<br>2.2<br>2.3                                                                                                                                                              | Environmental Requirements<br>Unpacking Instructions<br>Assembly Procedures                                                                                                                                                                                                                                                                                                                                                                                             | 2-1<br>2-2<br>2-4                                                                                               |

| 3                                                                                                                                                                              | OPERATING PROCEDURES                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1                                                                                                             |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.1.3<br>3.3.2<br>3.3.1.3<br>3.3.2<br>3.3.3<br>3.4<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3 | Processor Mini-Panel<br>Power Controls<br>Processor Operation Monitoring<br>Program Execution Control<br>Virtual Control Panel<br>Command Descriptions<br>Processor/CTU Interface<br>CTU Commands<br>Command Functions<br>Command Format<br>CTU Error Conditions<br>CTU Commands in MANIP<br>CTU Commands in DEBUG<br>Powering Up the System<br>Diagnostic Checks<br>Diagnostic Checks<br>Diagnostic Capabilities<br>Self-Test Operating Procedures<br>Self-Test Errors | 3-1 $3-3$ $3-4$ $3-5$ $3-7$ $3-10$ $3-10$ $3-11$ $3-12$ $3-13$ $3-14$ $3-16$ $3-19$ $3-20$ $3-20$ $3-20$ $3-20$ |

| 4                                      | INPUT/OUTPUT INTERFACES                                                                                                 | 4-1                          |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 4.1<br>4.1.1<br>4.1.2                  | Input/Output Bus Interface Signals<br>Input/Output Interface Signals<br>Backplane Pin Signal Connectors                 | 4-1<br>4-1<br>4-4            |

| 5                                      | INSTRUCTION REPERTOIRE                                                                                                  | 5-1                          |

| 5.1<br>5.2                             | Introduction<br>Octal Representation and Two's<br>Complement Notation                                                   | 5-1<br>5-1<br>5-3            |

| 5.3<br>5.4<br>5.4.1<br>5.4.1.1         |                                                                                                                         | 5-5<br>5-5<br>5-6            |

| 5.4.2<br>5.4.2.1<br>5.4.2.2            | Move Data Instructions<br>Jump and Modify Memory Instructions                                                           | 5-7<br>5-8<br>5-8<br>5-9     |

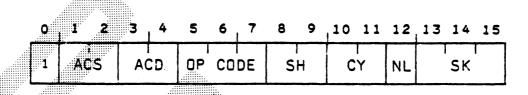

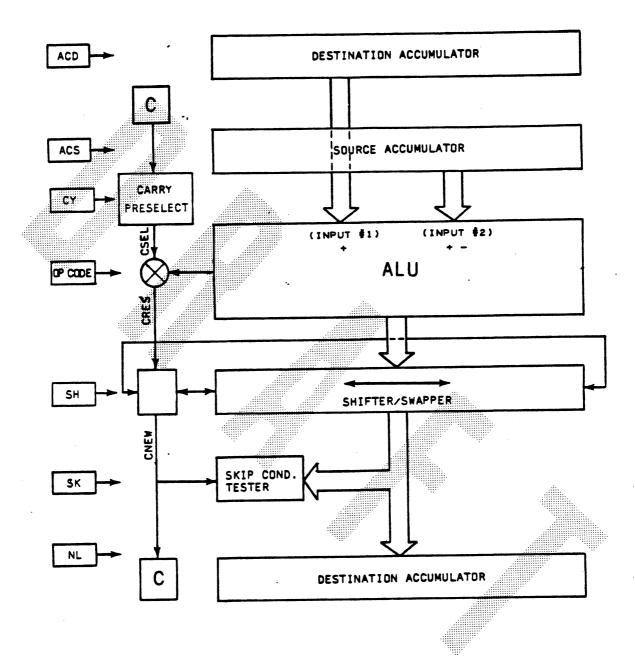

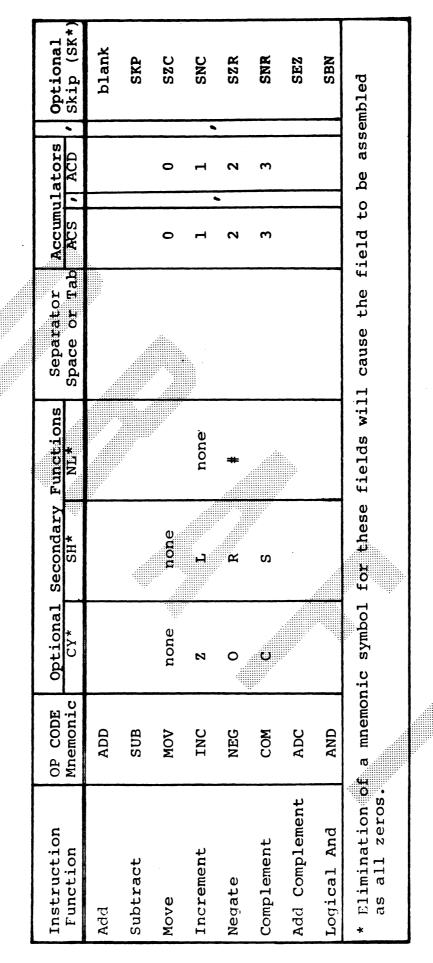

| 5.5<br>5.5.1                           | Arithmetic and Logic Processing                                                                                         | 5-10<br>5-12<br>5-12         |

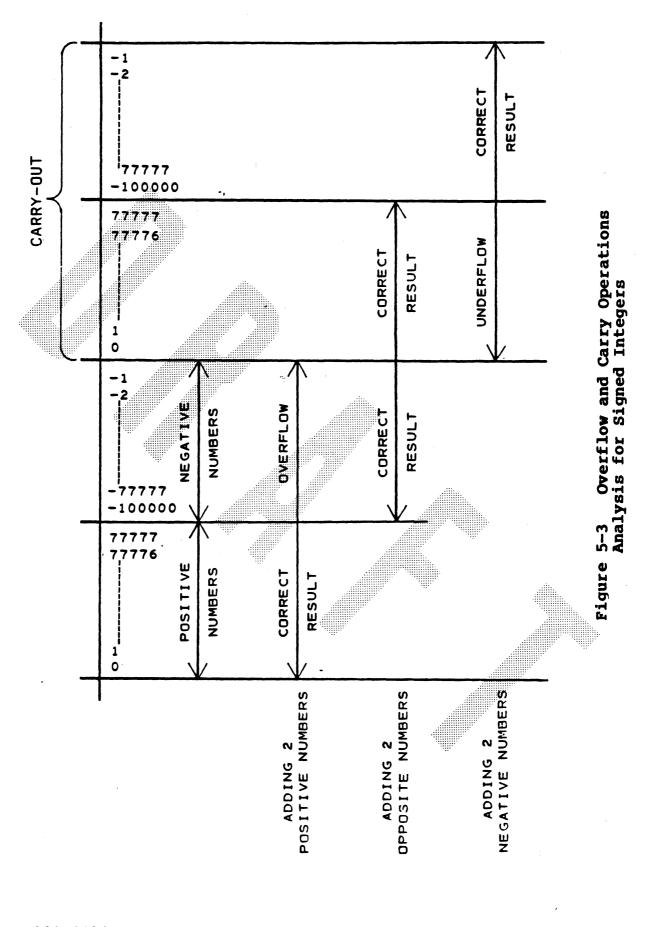

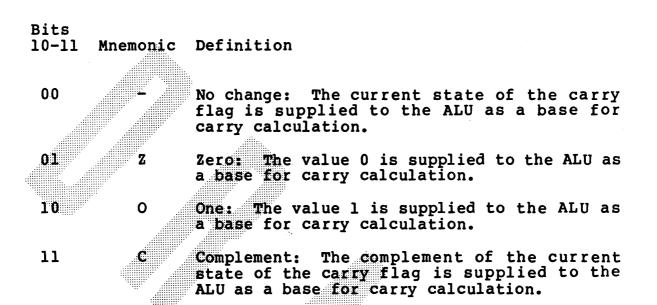

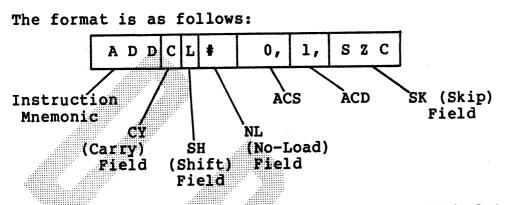

| 5.5.1.1<br>5.5.1.2<br>5.5.2<br>5.5.3   | Overflow and Carry-Out Operations<br>Arithmetic/Logic Functions<br>Secondary Functions                                  | 5-14<br>5-15<br>5-18<br>5-19 |

| 5.5.3.2<br>5.5.3.3                     | Shift Field (SH)<br>Carry Control Field (CY)<br>No-Load Field (NL)<br>Skip Control Field (SK)                           | 5-19<br>5-20<br>5-20<br>5-21 |

| 5.5.4<br>5.6                           | Assembler Language Conventions<br>and Examples<br>Input/Output Instruction Group                                        | 5-22<br>5-24                 |

| 5.6.1                                  | Programmed I/O Instructions<br>I/O Transfer and Device<br>Control Instructions                                          | 5-24                         |

| 5.6.1.2                                | Assembler Language Conventions<br>and Examples                                                                          | 5-27                         |

| 5.6.2<br>5.6.2.1<br>5.6.2.2<br>5.6.2.3 | Special Code 77 (CPU) Instructions<br>Special Mnemonics for CPU Instructions<br>Control Field Uses<br>Skip Instructions | 5-29<br>5-29<br>5-31<br>5-33 |

| 5.6.2.4                                | Assembler Language Conventions<br>and Examples<br>Instruction Execution Times                                           | 5-33<br>5-34                 |

| 5.7                                    | THEFTACTON PACAATON TIMES                                                                                               | 5 54                         |

DRAFT MARK III User Manual ٠

viii

| 6        | PERIPHERAL DEVICE HANDLING                            | 6-1          |

|----------|-------------------------------------------------------|--------------|

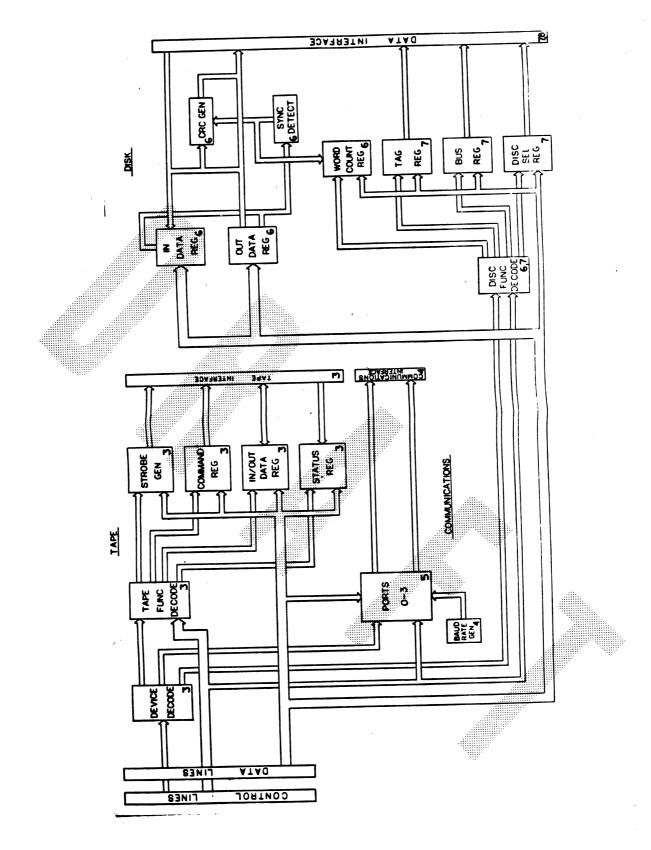

| 6.1      | Peripheral Interface Board                            | 6-1          |

|          | System Description                                    | 6-1          |

|          | Equipment Characteristics                             | 6-3          |

| 6.1.2.1  | Performance Characteristics                           | 6-3          |

| 6.1.2.2  |                                                       | 6-4          |

| 6.1.3    |                                                       | 6-4          |

| 6.2      | Input/Output Interface Handling                       | 6-6          |

| 6.2.1    |                                                       | 6-6          |

|          | Interrupt Sequence                                    | 6-7          |

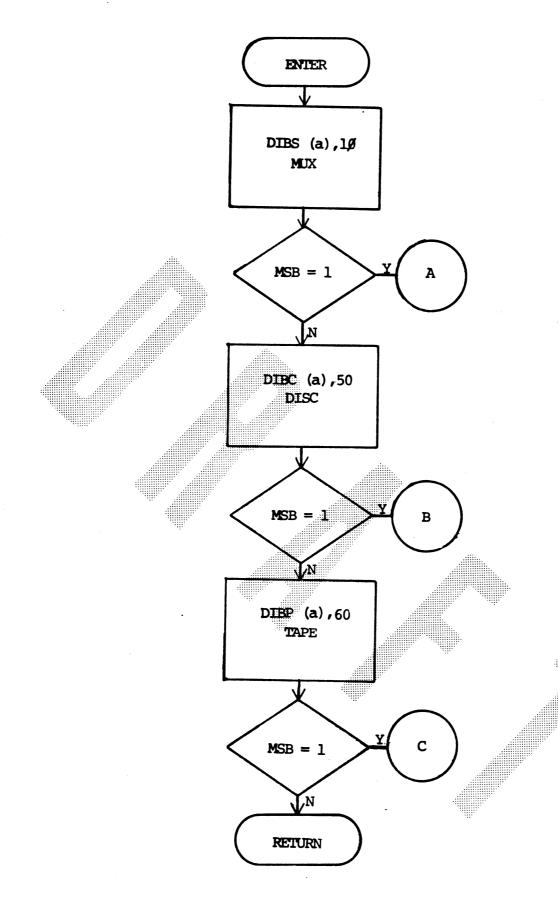

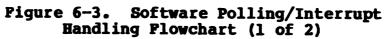

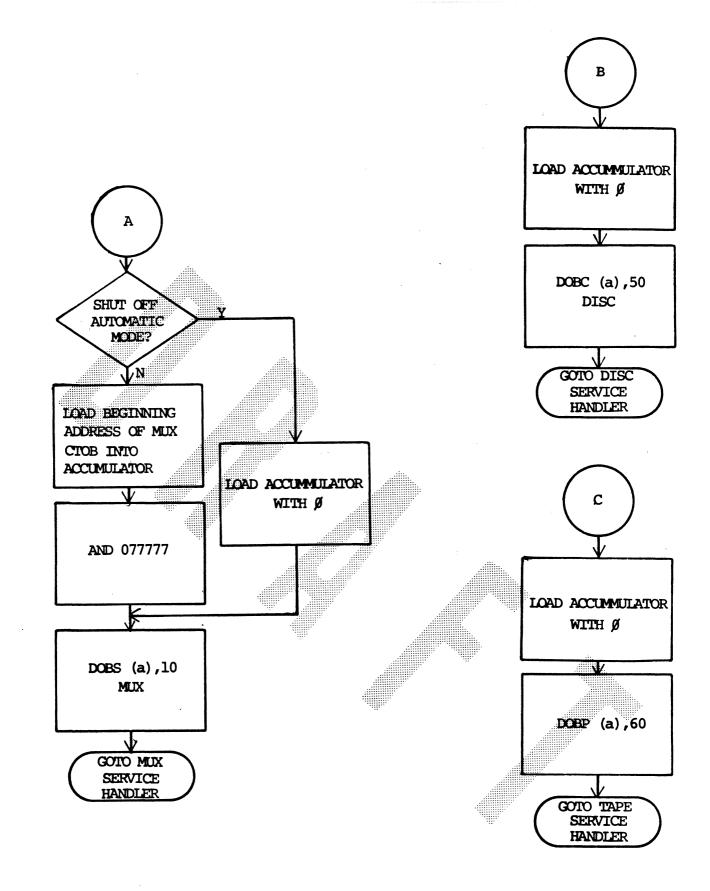

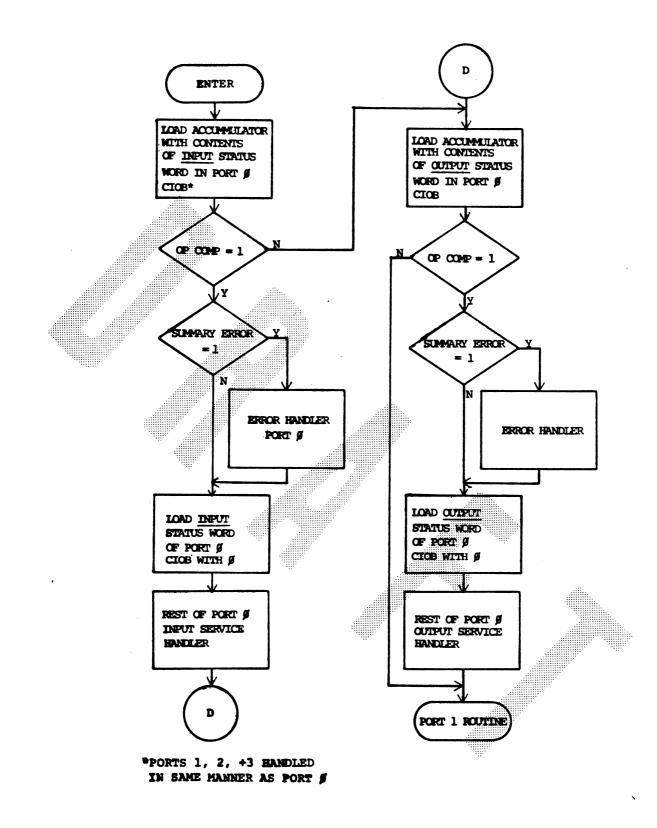

|          | Programming Polling and Interrupts                    | 6-8          |

|          | Programmed Transfers                                  | 6-14         |

| 6.2.2.1  | Master Terminal Interface                             | 6-14         |

| 6.2.3    |                                                       | 6-16         |

| 6.2.3.1  | Enabling/Disabling DMA Transfers                      | 6-17         |

| 6.2.3.2  | Initiating DMA Transfer                               | 6-18         |

| 6.2.3.3  | Turning Off Automatic Block Transfer                  |              |

|          | Mode for Disc or Tape                                 | 6-19         |

| 6.2.3.4  |                                                       |              |

|          | Mode for Multiplexer                                  | 6-19         |

| 6.3      |                                                       | 6-20         |

| 6.3.1    | MUX General Description<br>MUX Hardware Configuration | 6-21         |

| 6.3.1.1  | Baud-Rate Selection                                   | 6-21         |

| 6.3.1.2  |                                                       | 6-22         |

| 6.3.2    | Communications Byte Mode                              | 6-24         |

| 6.3.2.1  | Communications Controller IC 6850                     | 6-25         |

| 6.3.2.2  |                                                       | 6-25         |

| 6.3.2.3  | Standard Mode of Operation                            | 6-28         |

| 6.3.2.4  |                                                       | 6-28         |

| 6.3.2.5  |                                                       | 6-29         |

| 6.3.2.6  |                                                       | 6-33         |

| 6.3.3    |                                                       | 6-35         |

|          | MUX I/O Control Block                                 | 6-35         |

|          | Control Word Definitions                              | 6-35         |

| 6.3.3.3  |                                                       | 6-37<br>6-37 |

| 6.3.3.3. |                                                       | 6-42         |

|          | 2 Input Termination Status<br>3 Input Byte Pointer    | 6-43         |

| 6.3.3.3  |                                                       | 6-43         |

| 6.3.3.4  |                                                       | 6-44         |

| 6.3.3.4  |                                                       | 6-44         |

|          | 2 Output Termination Status                           | 6-49         |

|          | 3 Output Byte Pointer                                 | 6-50         |

| 6.3.3.4  |                                                       | 6-50         |

| 6.3.3.5  |                                                       | 6-51         |

| 6.3.3.5. |                                                       | 6-51         |

|          | 2 Initialization Guidelines                           | 6-52         |

|          | 3 Enabling/Disabling Ports and                        |              |

|          | Port Parameters                                       | 6-53         |

| 6.3.3.5. |                                                       |              |

|          | and Receivers                                         | 6-54         |

| 6.3.3.5. |                                                       | 6-56         |

| 6.3.3.6  | Deactivating MUX                                      | 6-56         |

|          |                                                       |              |

HM-080-0019-01 POINT 4 Data Corporation

DRAFT MARK III User Manual

ix

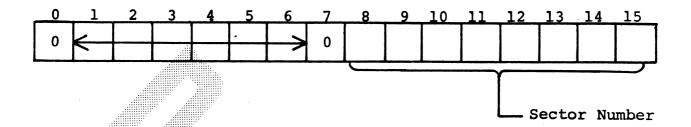

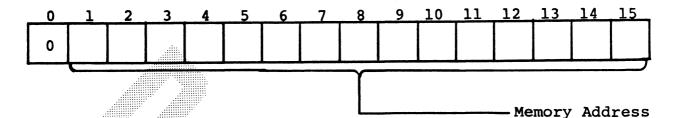

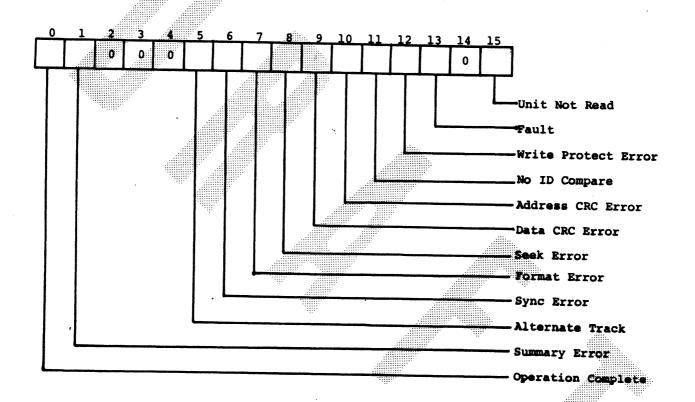

6.4 SMD/CMD Disc Interface 6.4.1 **Performance Characteristics** 6.4.2 Drive Requirements 6.4.3 Multi-Drive Connection 6.4.4 Operation 6.4.4.1 Sector Format Sector Verification 6.4.4.2 6.4.4.3 Data Transfer 6.4.4.4 File Linking 6.4.4.5 Data Verification 6.4.4.6 Error Checking and Status Reporting 6.4.4.7 Interrupt Operation 6.4.4.8 Initiating an Operation 6.4.4.9 Deactivating The Controller 6.4.4.10 Seek Control 6.4.4.11 Seek Error Recovery Input/Output Control Block 6.4.5 6.4.5.1 Opcode (Word 0) 6.4.5.2 Unit Select (Word 1) 6.4.5.3 Cylinder Select (Word 2) 6.4.5.4 Head Select (Word 3) 6.4.5.5 Sector Select (Word 4) 6.4.5.6 Sector Count (Word 5) Memory Address (Word 6) 6.4.5.7 Termination Status (Word 7) 6.4.5.8 6.4.6 Input/Output Instructions 6.4.6.1 Programmed I/O Input 6.4.6.2 Programmed I/O Output 6.4.6.3 Controller Command Input Controller Command Output 6.4.6.4 Write Data Operations 6.4.7 6.4.8 Read Data Operation 6.4.9 Read Verify Operation Read Regardless Operation 6.4.10 6.4.11 Formatting Operation 6.4.11.1 Memory Sector Block Description 6.4.11.2 Formatting Procedure 6.4.11.3 Format Considerations Programming Considerations 6.4.12

6-57 6-58

6-59 6-59

6-61

6-62

6-63

6-63

6-63

6-63

6-64 6-64

6 - 64

6-65 6-65

6-65

6-66

6-68

6-69 6-70

6-71

6-72

6-73

6-74

6-75

6-78

6-79

6-81 6-85

6-86

6-87

6-87

6-88

6-88

6-89

6-90 6-93

6-95

6-95

X

HM-080-0019-01

# FIGURES

| Number                 | Title                                                                               |      |                                       |        | <u>Page</u>     |

|------------------------|-------------------------------------------------------------------------------------|------|---------------------------------------|--------|-----------------|

| 1-1<br>1-2<br>1-3      | The POINT 4 MARK III Computer<br>Typical Configuration<br>POINT 4 MARK III Computer |      |                                       |        | 1-2<br>1-7      |

| 1-1                    | System Block Diagram                                                                |      |                                       |        | 1-10            |

| 2-1                    | POINT 4 MARK III Processor<br>Chassis Packaging                                     |      |                                       |        | 2-3             |

| 2-2                    | Power Supply Chassis and Processor<br>Chassis Mounting Slots                        | •    |                                       |        | 2-5             |

| 2-3                    | Typical POINT 4 MARK III<br>Board Configuration                                     |      |                                       | -<br>- | 2-6             |

| 3-1                    | POINT 4 Processor Mini-Panel                                                        |      |                                       |        | 3-2             |

| 4-1<br>4-2             | Input/Output Signals<br>Backplane I/O Signals                                       |      |                                       |        | 4-2<br>4-5      |

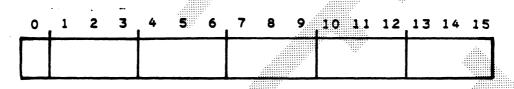

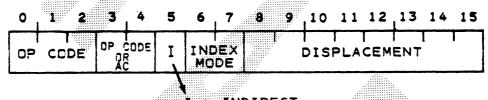

| 5-1<br>5-2             | POINT 4 Instruction Format Summary<br>Arithmetic/Logic Operations                   | •    |                                       |        | 5-4<br>5-13     |

| 5-3                    | Oveflow and Carry Operations Analys<br>for Signed Integers                          | 15   |                                       |        | 5-17            |

| 6-1<br>6-2             | Basic System Block Diagram<br>PIB Internal Architecture                             |      |                                       |        | 6-2<br>6-5      |

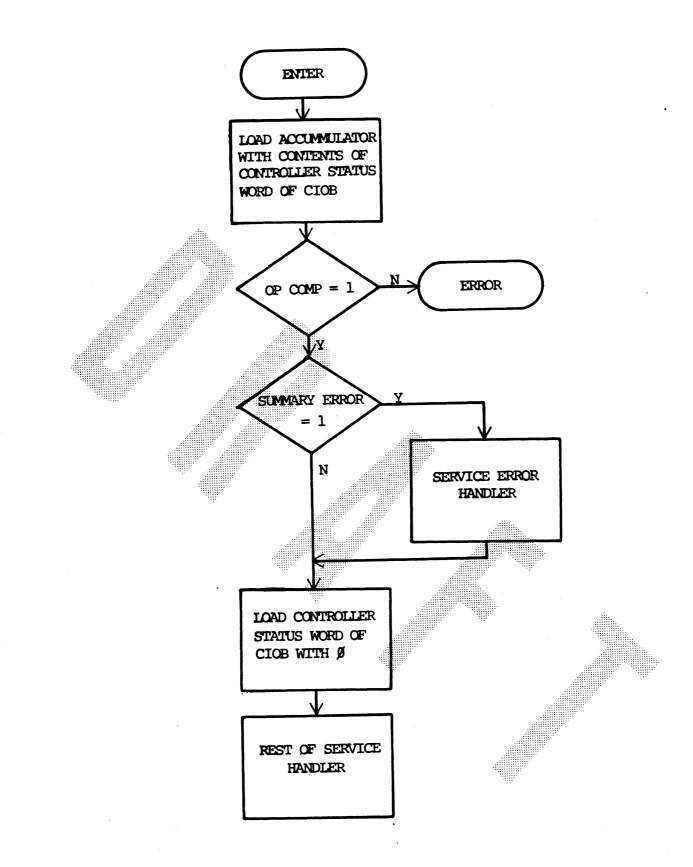

| 6-3                    | Software Polling/Interrupt<br>Handling Flowchart                                    |      | · · · · · · · · · · · · · · · · · · · |        | 6-10            |

| 6-4                    | I/O Service Routine Multiplexer<br>Handling Procedures                              |      |                                       |        | 6-12            |

| 6-5                    | I/O Service Routine Disc Tape<br>Handling Procedures                                |      |                                       |        | 6-13            |

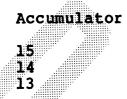

| 6-6                    | MARK III Asynchronous MUX/CRT<br>Cable Connector Wiring                             |      |                                       |        | 6-22            |

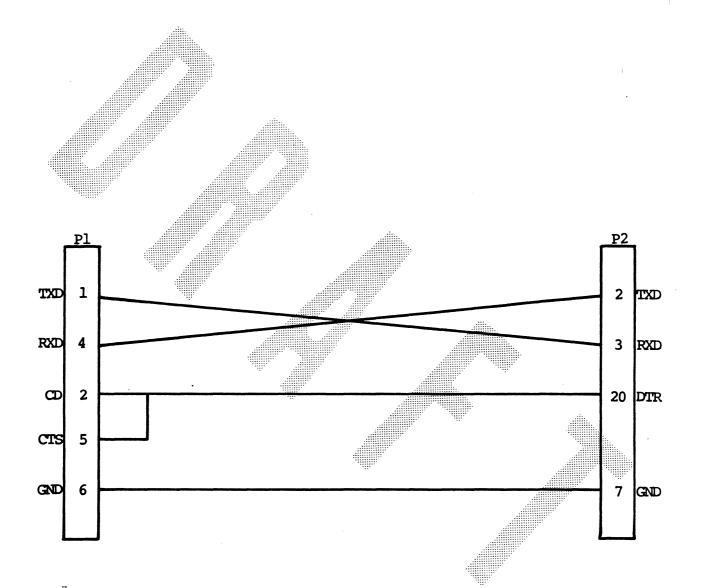

| 6-7                    | MARK III Asynchronous MUX/Line Prin<br>Cable Connector Wiring                       | ter  |                                       |        | 6-23            |

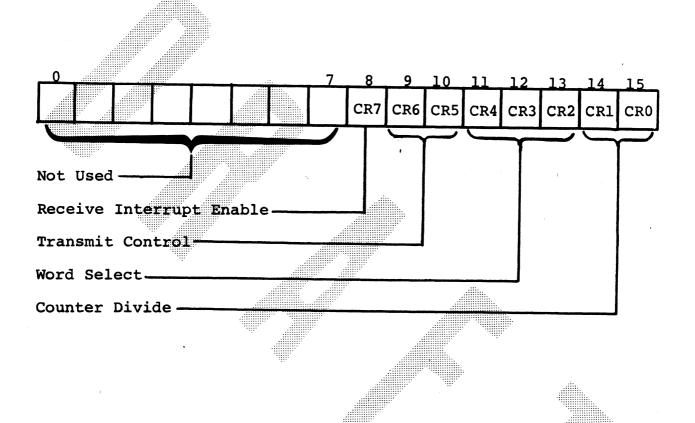

| 6-8<br>6-9             | Command Register on Port 0                                                          |      |                                       |        | 6-26<br>6-30    |

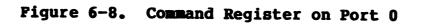

| 6-10                   | Status Register on Port O<br>Software Polling Flowchart                             |      |                                       |        | 0-30            |

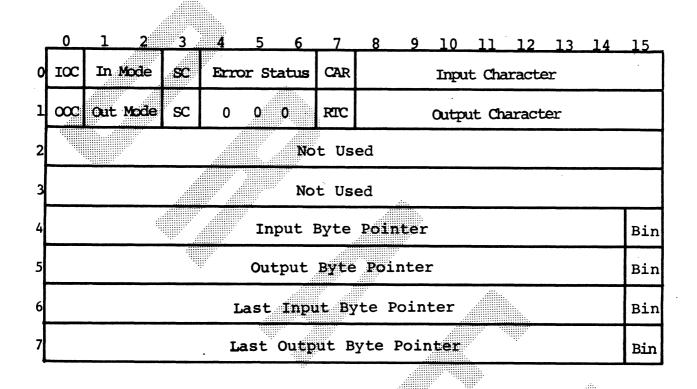

| 6-11                   | For Output Operations<br>MUX IOCB                                                   |      |                                       |        | 6-34<br>6-36    |

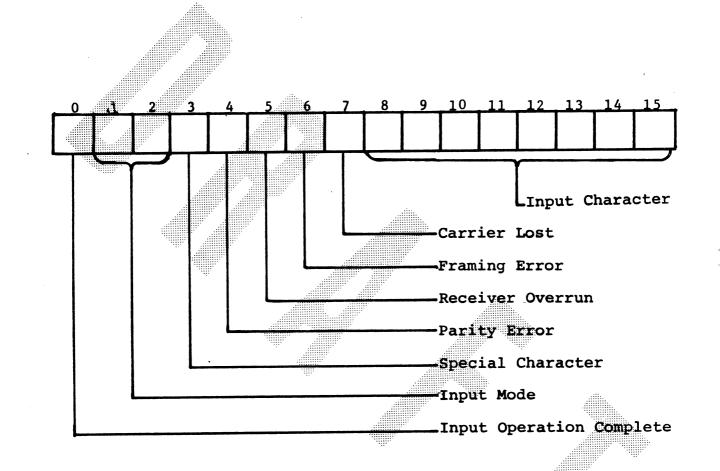

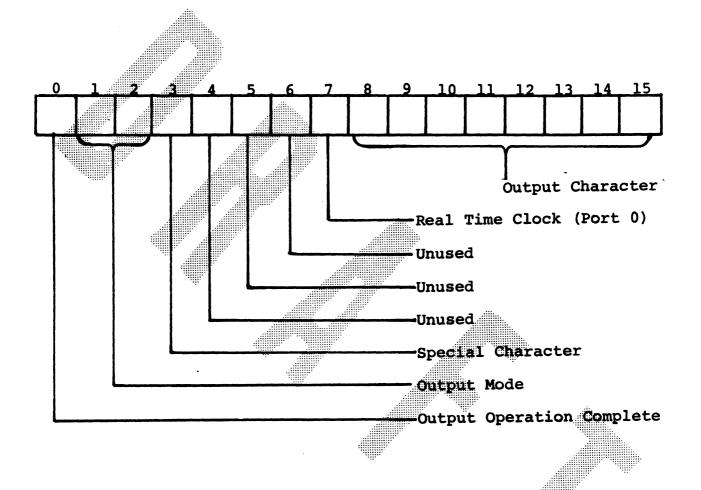

| 6-12<br>6-13           | Input Control Word - Word O<br>Output Control Word - Word l                         |      |                                       |        | 6-38<br>6-45    |

| 6-14                   | Transmitter/Receiver Example                                                        |      |                                       |        | 6-54            |

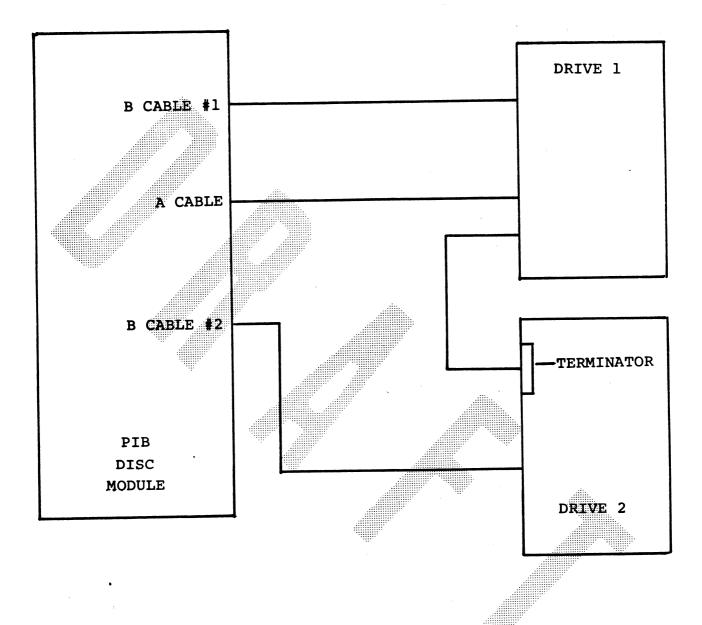

| 6-15                   | Daisy Chain Drive Connection                                                        |      |                                       |        | 6-60            |

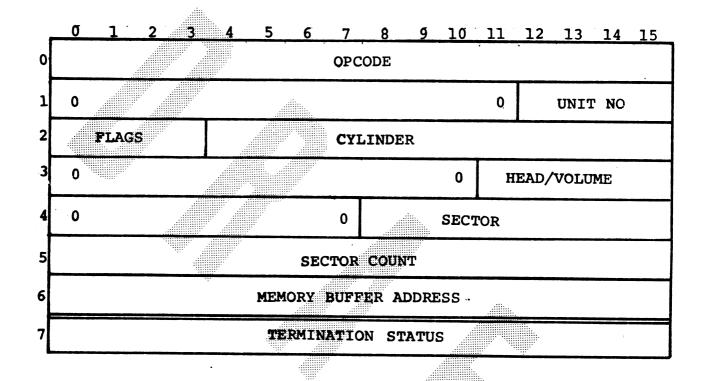

| 6-16<br>6-17           | Disc IOCB Format                                                                    |      |                                       |        | 6-67            |

| 6-18                   | Sector Table in Memory<br>Content of Each Block in The                              |      |                                       |        | 6-89            |

| J TO                   | Sector Block                                                                        |      |                                       |        | 6-90            |

| 6-19                   | Sector Format                                                                       |      |                                       |        | 6-92            |

| 6-20                   | Format IOCB Example                                                                 |      |                                       |        | 6-93            |

| HM-080-00<br>POINT 4 I | )19-01<br>Data Corporation xi                                                       | MARK | III                                   | User   | DRAFT<br>Manual |

ļ ١

# TABLES

# Number

# **Title**

$\mathbf{v}_{0,g} \phi^{j}$

4

٢

| 3-1<br>3-2 | Power Control Switch Functions<br>Power OK LED Interpretations | 3-3          |

|------------|----------------------------------------------------------------|--------------|

| 3-3        | Summary of MANIP Command Functions                             | 3-5          |

| 3-4        | MANIP Commands                                                 | 3-8          |

| 3-5        | CTU Command Functions                                          | 3-11         |

| 3-6        | CTU Error Codes                                                | 3-13         |

| 3-7        | CTU Commands in MANIP                                          | 3-14         |

| 3-8        | CTU Commands in DBUG                                           | 3-16         |

| 3-9        | Summary and Overview of Data                                   |              |

|            | Transfer Commands                                              | 3-18         |

| 4-1        | Input/Output Signals by                                        |              |

| ••         | Classification                                                 | 4-3          |

|            |                                                                |              |

| 5-1        | Indexing Modes                                                 | 5-6          |

| 5-2        | Move Data Instructions                                         | 5-8          |

| 5-3        | Jump and Modify Memory Instructions                            | 5-9          |

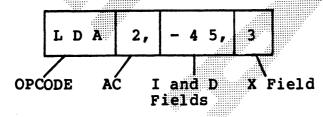

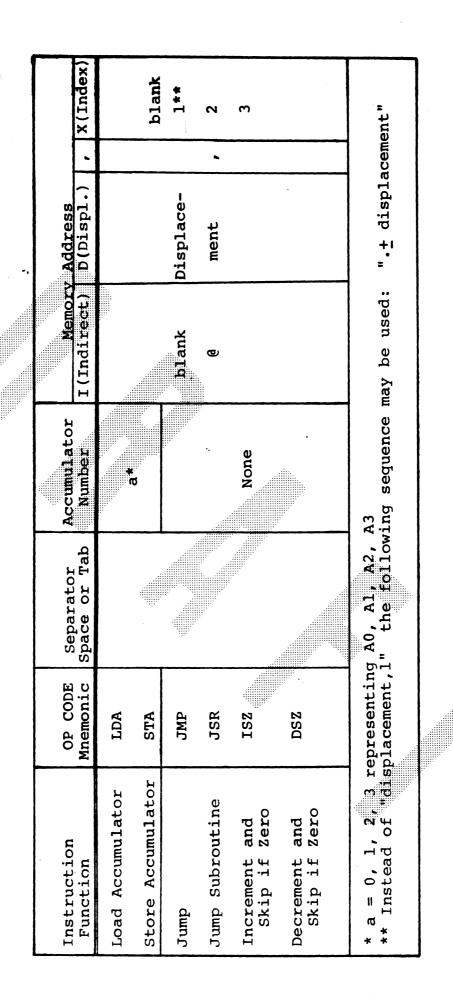

| 5-4        | Assembler Language Conventions for                             |              |

|            | Memory Reference Instructions                                  | 5-11         |

| 5-5        | Arithmetic LOgic Instructions                                  | 5-18         |

| 5-6        | Shift Field Functions                                          | 5-19         |

| 5-7        | Carry Control Field Functions                                  | 5-20         |

| 5-8        | Skip Control Field Functions                                   | 5-21         |

| 5-9        | Assembler Language Conventions for                             |              |

|            | Arithmetic and Logic Instructions                              | 5-23         |

| 5-10       | I/O Transfer Instructions                                      | 5-26         |

| 5-11       | Assembly Language Conventions for                              |              |

|            | Input/Output Instructions                                      | 5-28         |

| 5-12       | Special CPU I/O Instructions                                   | 5-30         |

| 5-13       | Control Field Definitions for 1/0                              | F 20         |

|            | Instructions with Device Code 77                               | 5-32<br>5-33 |

| 5-14       | Skip Instructions                                              | 5-33<br>5-34 |

| 5-15       | Instruction Execution Times                                    | 9-34         |

| 6-1        | Baud-Rate Configuration                                        | 6-21         |

| 6-2        | Port Assignments for Baud Rate Headers                         | 6-21         |

| 6-3        | DOA, DIA Device Codes                                          | 6-24         |

| 6-4        | Command Register Bit Functions                                 | 6-27         |

| 6-5        | Status Register Bit Operations                                 | 6-32         |

| 6-6        | Input Control Word Definit                                     | 6-39         |

| 6-7        | Output Control Word Definitions                                | 6-46         |

| 6-8        | Enabling/Disabling Operation                                   | 6-55         |

| 6-9        | Disc IOCB Word 4 Definition                                    | 6-68         |

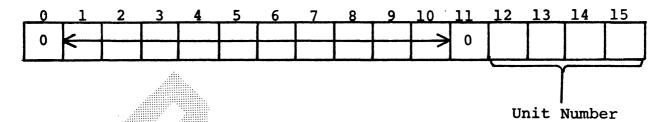

| 6-10       | Disc IOCB Word 1 Definition                                    | 6-69         |

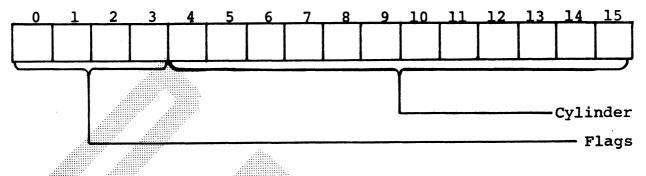

| 6-11       | Disc IOCB Word 2 Definition                                    | 6-70         |

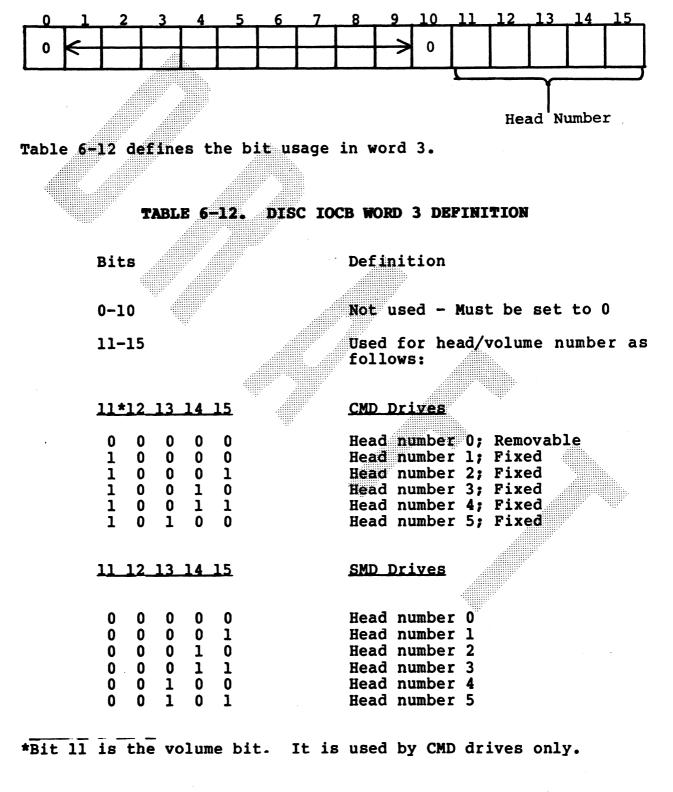

| 6-12       | Disc IOCB Word 3 Definition                                    | 6-71         |

| 6-13       | Disc IOCB Word 4 Definition                                    | 6-72         |

| 6-14       | Disc IOCB Word 5 Definition                                    | 6-73         |

| 6-15       | Disc IOCB Word 6 Definition                                    | 6-74         |

| 6-16       | Disc Termination Status Definition                             | 6-76         |

|            |                                                                |              |

xii

DRAFT MARK III User Manual

| 6-17 | DIA Instruction Accumulator Bits | 6-80 |

|------|----------------------------------|------|

| 6-18 | DOA Instruction Accumulator Bits | 6-82 |

| 6-19 | TAG 3 Bit Functions              | 6-84 |

| 6-20 | Memory Sector Block Fields       | 6-91 |

DRAFT MARK III User Manual

xiii

### SECTION 1

# INTRODUCTION AND GENERAL DESCRIPTION

#### 1.1 SCOPE

This manual provides general reference information, including system description, equipment specifications, description of the instruction set, interface data, and installation and operation information for the POINT 4 MARK III Computer. This manual is designed to be a general reference guide for both the programmer and the operator, and as such contains both detailed information to familiarize the user with the system, and charts for use as quick reference material.

The manual is organized into six sections, as summarized below:

| Section I   | Introduction and system architecture description  |

|-------------|---------------------------------------------------|

| Section II  | Installation methods                              |

| Section III | Operating procedures and<br>diagnostic guidelines |

| Section IV  | System interface signals                          |

| Section V   | Instruction set                                   |

| Section VI  | Peripheral interface guidelines                   |

#### 1.2 GENERAL DESCRIPTION

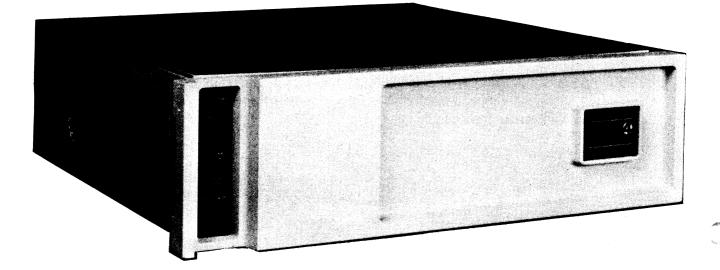

The POINT 4 MARK III Computer is a 16-bit, high-speed, general purpose minicomputer with a versatile instruction set. The POINT 4 MARK III employs a novel design architecture to achieve the simplicity and flexibility of a microprogrammed design and the speed of a hard-wired logic design. In addition the design allows direct addressing of up to 32K words of MOS random access memory. These features make the POINT 4 MARK III Computer well suited to OEM applications in business data systems, and control systems. See Figure 1-1 for a photograph of the POINT 4 MARK III Computer.

# Figure 1-1. The POINT 4 MARK III Computer

HM-080-0019-01 POINT 4 Data Corporation 1-2 MARK III User Manual

INTRODUCTION

# 1.2.1 PEATURES

The POINT 4 MARK III Computer includes the following features:

- o CPU and 64 bytes of RAM on the same board

- o Peripheral Interface Board (PIB) with built-in Multiplexer, printer, disc, and tape interfaces

- o Up to four asynchronous ports, baud-rate selectable to 9600 baud

- o Up to two sector-mark signal type SMD/CMD drives

- o Up to four streamer tape drives

- o Disc transfer rates to 1.25 megabytes per second

- o Virtual control panel

- o Internal power supply for CPU and PIB boards

INTRODUCTION MARK III User Manual

# 1.3 EOUIPMENT CHARACTERISTICS

# 1.3.1 PERFORMANCE CHARACTERISTICS

Word Length: General Purpose Accumulators: Memory Cycle Time: RAM Access Time: Microprogram Cycle Time: Memory:

DMA for Disc Controller Input -Output - 16-bits 4 600 nanoseconds Hu 200 nanoseconds 64K bytes

1200 nanoseconds per word 1200 nanoseconds per word

DMA for Multiplexer Automatically vectored byte access -10 microseconds per byte

Interrupt Response:

2000 nanoseconds

Backplane:

100-pin edge connector

# 1.3.2 EQUIPMENT SPECIFICATIONS

| POWER SUPPLY                                    |

|-------------------------------------------------|

| AC Voltages:                                    |

| 105 to 125 VAC, 5 amps max. 47 to 63 Hz         |

| 210 to 250 VAC, 2.5 amps max, 47 to 63 Hz       |

| Voltages Provided:                              |

| +5V @ 20A                                       |

| -5V @ .5A                                       |

| +12V @ 1.5A                                     |

| -12V @ .1A                                      |

|                                                 |

| OPERATING ENVIRONMENT                           |

| Ambient Temperature Range: 0-122F (0-50C)       |

| Relative Humidity: 10 to 90% noncondensing      |

|                                                 |

| MECHANICAL                                      |

| Processor Chassis                               |

| Dimensions - 5.25 inches high                   |

| 19.0 inches wide                                |

| 17.5 inches deep                                |

| 17.5 inches deep<br>(14 cm x 48.3 cm x 44.5 cm) |

| Weight: 30 pounds (13.5 kilograms)              |

|                                                 |

| CPU/Memory PCB                                  |

| Dimensions: 14.5" x 12"                         |

| (36.8 cm x 30.5 cm)                             |

|                                                 |

| Peripheral Interface Board                      |

| Dimensions: 14.5" x 12                          |

| (36.8 cm x 30.5 cm)                             |

|                                                 |

| Power Supply Board                              |

| Dimensions: 14.5" x 12"                         |

| (36.8 cm x 30.5 cm)                             |

|                                                 |

|                                                 |

|                                                 |

|                                                 |

|                                                 |

|                                                 |

| · 1                                             |

|                                                 |

HM-080-0019-01 POINT 4 Data Corporation 1-5

Þ

# **1.4 SYSTEM ARCHITECTURE**

TO BE SUPPLIED

HM-080-0019-01 POINT 4 Data Corporation

1-7

INTRODUCTION MARK III User Manual

# 1.4.1 SYSTEM FUNCTIONAL UNITS

TO BE SUPPLIED

# 1.4.1.1 Central Processor and Memory Board

The Central Processor board contains all basic elements of the CPU:

- o 2903 Bit Slice Microprocessor (4 bits wide) containing four general-purpose accumulators, plus 12 special-purpose registers and arithmetic logic functions

- o Microprogrammed Control Store

- o Instruction Register

- o Main Data Bus

- o Program Counter

- o Effective Address Register

o Timing Control

- o Input/Output Control

- o 32K Words of Random Access Memory (RAM)

- o CRC Error Detection Logic for Disc Drive Interface

- o APL PROM containing a program to implement Virtual Control Panel Features, and the Self Test

Figure 1-3 is a block diagram of the POINT 4 MARK III system, showing logic to handle each of the above functions.

HM-080-0019-01 POINT 4 Data Corporation INTRODUCTION MARK III User Manual

# Figure 1-3. POINT 4 MARK III Computer System Block Diagram

HM-080-0019-01 POINT 4 Data Corporation

1-10

INTRODUCTION MARK III User Manual

# 1.4.1.2 Processor Chassis and Pront Panel

The POINT 4 MARK III processor chassis is designed to be mounted in a standard 19-inch equipment rack. The 3-slot processor chassis is 5.25 inches high, 19 inches wide and 17.5 inches deep.

Cooling is provided by two fans mounted on the left side of the chassis behind the Mini-panel.

The front panel snaps on and off. There are no screws or hinges holding it in place. No cabling exists between the front panel and the chassis since the Mini-panel is mounted directly onto the chassis and its controls are accessible through a slot on the left side of the front panel.

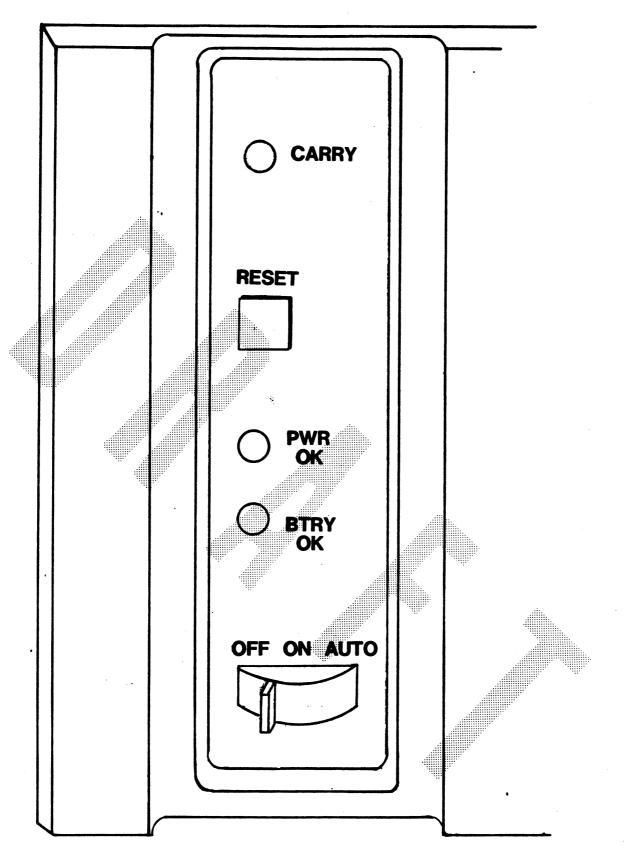

# 1.4.1.3 Processor Mini-Panel

The Mini-Panel on the POINT 4 MARK III chassis houses 2 sets of controls and indicators for basic processor operation. Controls and indicators are located on the left side of the chassis, as indicated in Figure 1-5. The Mini-Panel is capable of three operating functions: processor monitoring indicators, program execution controls, and power controls and indicators. For further detail, see Section 3.1 on Mini-Panel operations.

The Virtual Control Panel allows monitoring and control of the processor from a master terminal, using the manipulator program MANIP. For further details see Section 3.2 on Virtual Control Panel operations.

HM-080-0019-01 POINT 4 Data Corporation

1-11

INTRODUCTION MARK III User Manual

# 1.4.1.4 Power Supply Board

The power supply is packaged on a single board (14.5" wide, 12" deep, and 2" high) with protective cover. It plugs directly into the MARK III backplane. Input voltage requirements and power supply output voltages are:

- 1. AC INPUT

- 1.1 Voltage: 117 VAC + 10% 15% 234 VAC + 10% - 15% (jumper programmed)

- 1.2 Frequency: 47 63 HZ

- 1.3 Power: 180 VA maximum

- 1.4 Inrush Current: 12 amps peak

- 2. DC OUTPUTS

- 2.1 Voltages:

- + 5 VDC @ 20 amps

- 5 VDC @ 0.5 amps

- + 12 VDC @ 1.5 amps

- 12 VDC @ 0.1 amps

#### SECTION 2

#### INSTALLATION

#### 2.1 ENVIRONMENTAL REOUIREMENTS

The location in which the POINT 4 MARK III Computer will be used must be evaluated prior to installation, to ensure that all power and cooling requirements are met. The following pre-installation considerations are necessary:

- Power Requirements: The POINT 4 MARK III requires a power source of 105 to 125 VAC, 47 to 63 Hz with 5 amperes maximum current draw; or a 210 to 250 VAC, 47 to 63 Hz power source with 2.5 amperes current draw. In addition to power requirements for the POINT 4 MARK III, consideration must be made of power resources and electrical outlets to handle all peripheral devices to be used with the processor.

- Temperature Requirements: The POINT 4 MARK III requires an environment with an adequate temperature control system to maintain a recommended 20 to 30 degrees Celsius. Maximum operating range is between 0 and 50 degrees Celsius. Relative humidity is 10 to 90 pecent, noncondensing.

- Enclosure Requirements: The POINT 4 MARK III is packaged in a 3-slot chassis, measuring 5.25 inches high, 19 inches wide, and 17.5 inches deep. The CPU/Memory PCB, Peripheral Interface Board, and Power Supply Board have the same dimensions: 14.5" x 12".

# 2.2 UNPACKING INSTRUCTIONS

TO BE SUPPLIED

HM-080-0019-01 POINT 4 Data Corporation

INSTALLATION MARK III User Manual

Figure 2-1. POINT 4 MARK III Processor Chassis Packaging

HM-080-0019-01 POINT 4 Data Corporation

2-3

INSTALLATION MARK III User Manual

### 2.3 ASSEMBLY PROCEDURES

The following assembly procedures are required for MARK III installation.

- 1. Plug AC cord into back of chassis.

- 2. Unscrew the four screws holding the top panel on the back of the chassis. This allows access to the Peripheral Interface Board, second board from the top).

- 3. On the PIB, plug CRT cable into connector J5. This is the first white Molex connector to the left of the four connectors.

- 4. Pull the white tabs at both corners of the board. Pull out board approximately 2 or 3 inches.

- 5. To connect the disc drive:

- a. Plug into connector J6 (60 pin, left side of PIB), Cable "A", with pin 1 of cable to the right edge.

- b. Plug into connector J8 (26 pin, behind J6), Cable "B", with pin 1 of cable to the right edge.

- c. If a second drive is to be connected, the second "B" cable will plug into J7 (to the right of J8).

- 6. To connect the streamer tape drive, plug the 50-pin cable into Jl (right side of PIB) with pin 1 to the right edge.

CAUTION

Jl has no cable guides. Make sure cable is not shifted to right or left.

- 7. To connect a printer, plug its cable into either **J3** or J2 (white, 6-pin Molex).

- 8. The remaining port may be used for another CRT terminal.

- 9. All the MUX ports are strapped for 9600 baud rate. They may be restrapped if another rate is desired.

- 10. Push the PIB back into the chassis.

- 11. Power is turned on via an ON/OFF switch in the back of the chassis. With power ON, the red light below the switch is illuminated.

- 12. Proceed to Powering Up the System, Section 3.4.

10

# Figure 2-2. Power Supply Chassis and Processor Chassis Mounting Slots

HM-080-0019-01 POINT 4 Data Corporation

2-5

INSTALLATION MARK III User Manual

TO BE SUPPLIED

Figure 2-3. Typical POINT 4 MARK III Board Configuration

HM-080-0019-01 POINT 4 Data Corporation INSTALLATION MARK III User Manual

# Section 3

## **OPERATING PROCEDURES**

#### 3.1 PROCESSOR MINI-PANEL

There are two types of control units available on the POINT 4 MARK III Computer. These control units are:

- o Processor Mini-Panel

- o Virtual Control Panel

Controls and indicators are butlined and specific procedures for performing common types of operations are given in the following subsections.

The POINT 4 MARK III processor chassis houses essential controls and indicators for basic processor control functions. The controls and indicators for this processor Mini-panel are located on the left-hand side of the chassis (see Figure 1-1). There are three types of operating functions on the Mini-panel: processor monitoring indicators, program execution controls and power controls and indicators. Figure 3-1 is an illustration of the processor Mini-panel controls and indicators.

OPERATING PROCEDURES MARK III User Manual

Figure 3-1. POINT '4 Processor Mini-Panel

## 3.1.1 POWER CONTROLS

The Mini-panel contains power controls and indicators. POWER ON is controlled by a three-position switch. Table 3-1 lists the three functions of the power switch.

Also provided is a Light Emitting Diode (LED) indicator, which illuminates to indicate an active state for AC power.

Table 3-2 shows the interpretations of the POWER OK LED.

See Figure 3-1 for positions of the three-position switch and the POWER ON indicator.

## TABLE 3-1. POWER CONTROL SWITCH FUNCTIONS

Switch Setting

Function

ON

Turns on power to the processor and places the Mini-panel in the Panel-On Mode. In this mode all controls and indicators on the Mini-panel are enabled. One pass of Self-test is executed, the carry light illuminates once and goes off, and the message OK is displayed on the port 0 terminal.

- AUTO Functions the same as ON for POINT 4 MARK III.

- OFF

- Turns off the power supply and thus all processor functions.

# TABLE 3-2. POWER OK LED INTERPRETATIONS

POWER OK

#### Interpretation

OFF Power supply not connected to AC.

- OFF This condition (if keyswitch is in ON or AUTO) indicates that one of the power supply voltages is out of tolerance.

- ON All power supply voltages are in tolerance and available to the processor chassis.

# 3.1.2 PROCESSOR OPERATION MONITORING

In addition to the power monitoring indicators discussed above, the Mini-panel has an LED indicator for monitoring the carry state of processor operation. This LED functions as follows:

Indicates the current state of the processor carry flag. The LED illuminates when the carry flag is set to a l.

See Figure 3-1 for location of the carry indicators.

## 3.1.3 PROGRAM EXECUTION CONTROL

A pushbutton switch is available to reset program execution in the processor. This switch is enabled in the Panel-On Mode (power switch set to ON or AUTO position) and disabled in the Panel-Off Mode (power switch set to OFF position). RESET functions as follows:

The RESET switch loads contents of an octal debugger/manipulator/Self-test PROM into top 1000 (octal) words of memory. The debugger/manipulator is used for access to accumulators and memory. Allows examination and deposit of data for operation monitoring and control. It optionally allows loading of system software from disc. See Section 2.5 for debugger/manipulator program commands.

See Figure 3-1 for location of the RESET switch.

HM-080-0019-01 POINT 4 Data Corporation OPERATING PROCEDURES MARK III User Manual

#### 3.2 VIRTUAL CONTROL PANEL

The POINT 4 MARK III has the ability to do front panel operations plus some system monitoring functions from a master terminal. This feature is designed for use by programmers to debug system problems and to manipulate the contents of registers and memory. The feature is implemented in a system program called MANIP which is loaded into RAM from a PROM when the RESET switch is pressed.

MANIP is a position-independent memory manipulator and debug package. MANIP occupies only 1000 (octal) words of memory.\* All operations are executed by typing one letter followed by octal parameters as required (except colon (:) which is also preceded by an octal parameter) and ending with a RETURN.

Table 3-3 lists the functions provided by MANIP (the number in parentheses indicates the number of parameters required for that particular function).

|      | TABLE 3-3. SUNMARY OF MANIP COMMAND FUN           | CTIONS                 |

|------|---------------------------------------------------|------------------------|

| Code | Function                                          | Parameters<br>Required |

| A    | Type initial PC, accumulators and carry flip-flop | (0)                    |

| С    | Change accumulator or carry flip-flop             | (2)                    |

| D    | Dump (octal, word or byte)                        | (1 or 2)               |

| J    | Jump with accumulators and carry restored         | (l or 2)               |

| K    | Store a constant in a block of memory             | (3)                    |

| M    | Move a block in memory                            | (3)                    |

| P    | Program load from disc                            | (0 or 1)               |

| R    | Read 3 blocks from CTU                            |                        |

| T    | Run Self-test program                             | (0)                    |

| :    | Examine or deposit into a specified location      | (2)                    |

\*For those who are familiar with POINT 4's IRIS Operating System, MANIP is comparable to DBUG. The main differences are that MANIP does not have (1) symbolic capability, (2) breakpoints or trace, (3) disc read or write, and (4) Ctrl H/Ctrl A (backspace) capability. MANIP occupies only 1000 (octal) words of memory, while DBUG occupies 3000 (octal) words of memory.

HM-080-0019-01 POINT 4 Data Corporation

These functions are described in detail in the following subsections.

MANIP normally occupies the memory locations 77000 through 77777. Location 77000 is reserved for saving the initial value of the program counter (PC), that is, the value of PC where the CPU had halted before MANIP was started. MANIP may be moved at any time by use of its MOVE (M) instruction. The carry light flashes while MANIP is waiting for an input character to be entered. This is a signal that MANIP is active and will respond to input.

If an error is made while entering control information, two choices are available for correcting it.

- 1. Press ESC (or any other control character except RETURN) to delete the type-in and enable a new type-in.

- 2. If the error was in entering an octal value, type a few zeros followed by the correct octal number, as MANIP only uses the last six octal digits typed in for the octal word.

OPERATING PROCEDURES

## 3.2.1 COMMAND DESCRIPTIONS

A MANIP command consists of a single letter which is the command identifier and parameters which specify addressing modes, memory addresses and data input. All parameters must be entered in octal form. The letters x, y, z, a, m, and n are used on the following pages to represent octal parameters. Press the RETURN key after entering any command. Table 3-4 lists all MANIP commands and their functions.

See Appendix D for a summary chart of MANIP commands.

# TABLE 3-4.MANIP COMMANDS

Command & Parameters

## Definition

A

Causes initial value of PC (program counter) saved in first location of MANIP, contents of accumulators A0, A1, A2, A3, and carry flip-flop as they were at the time MANIP was entered to be typed on the master terminal screen.

Cx,y

Change accumulator or carry flip-flop.

- o If x is 0, 1, 2, or 3, n y is stored as saved value for accumulator x (A0, A1, A2, A3, respectively).

- o If x is 4, then saved value of the carry

flip-flop is set to 0 or 1 according as y

is 0 or not.

- o If x is greater than 4 and an address offset has been established (see F command), x is interpreted as a real address using the offset previously established, and typed out on the master terminal. The y parameter is not used in this case.

- o Parameter Description

- x 1 octal digit 0-7

- y 1 octal word

Dx

Dump memory in octal, beginning at location x, using addressing mode a. Eight words (or bytes if a byte address mode is used) are typed per line, with the address of the first word (byte) at the beginning of each line.

o Parameter Description

x - an octal number representing a 16-bit memory address

Jx

- Jump to location x (using addressing mode a) with accumulators and carry stored.

- o Parameter Description

- x an octal number representing 16-bit memory address

- **Kx,y,z** Store the octal constant z in locations x through y, inclusive.

o Parameter Description

- x octal number representing 16-bit beginning memory address

- y octal number representing 16-bit ending memory address

- z octal number representing constant

## TABLE 3-4. MANIP COMMANDS (Cont)

Command & Parameters

# Definition

Mx,y,z

Move block in memory. Locations x through y, inclusive, are moved to area starting at location z.

- o Source and destination areas may overlap in either direction without bad effects.

- o May be used to move MANIP itself as long as destination area does not overlap source area.

- o Parameter Description

- x octal number representing 16-bit beginning memory address

- y octal number representing 16-bit ending memory address

- z octal number representing 16-bit beginning memory address of new location

Initial Program Load from disc (Sector 0, Surface 0, Cylinder 0). Performs standard bootstrap APL function (i.e., gives an NIOS instruction and then idles at location 377 waiting for the disc to overwrite that location).

Read blocks 2, 3 and 4 from the Cassette Tape Unit (CTU) tape. Bootstrap will run automatically. After the R Command has been given, the only valid functions are the Jump (J) Command and/or any CTU command. See Subsection 3.3.2 for description of CTU commands in MANIP for use in CTU mode.

Run the Self-test program. Sucessful completion results in OK being displayed on port 0 terminal. Self-test then moves itself randomly in memory and repeats the above. Main memory will be destroyed. See the POINT 4 MARK III Diagnostics Manual for further details.

x:y

- Octal value y is stored at location x, and next cell is opened.

- o Parameter Description

- x octal number representing 16-bit memory address

- y 1 to 6 digits representing an octal value

HM-080-0019-01 POINT 4 Data Corporation

3-9

R

Ρ

Т

### 3.3 PROCESSOR/CTU INTERFACE

This section describes commands used to transfer stand-alone programs such as diagnostics between the CTU and the POINT 4 MARK III. There are sixteen basic CTU commands which can be enabled from the master terminal. DBUG (POINT 4's stand-alone debug program) can perform all sixteen commands; MANIP (the Virtual Control Panel program built into POINT 4 MARK III) can perform only a subset of the CTU commands. Section 3.3.2 describes CTU commands enabled in MANIP; Section 3.3.3 describes those enabled in DBUG.

#### 3.3.1 CTU COMMANDS

A CTU command consists of a single character control code (CTRL and an ASCII character), a block number for the starting block, an additional block count and a RETURN. There are sixteen functions which can be specified by control codes from an ASCII keyboard.

OPERATING PROCEDURES MARK III User Manual

# 3.3.1.1 Command Functions

The control code of a CTU command is a single nonprinting character entered while holding down the CTRL key on the keyboard. The CTU will echo two printable characters, a caret for the control key and the ASCII letter representing the command for ease or command verification. The CTU command functions are listed in Table 3-5.

| Function         | Control Code | CTU ASCII Echo |

|------------------|--------------|----------------|

| Read Blocks      | CTRL R       | ^R             |

| Write Blocks     | CTRL W       | ^w             |

| Seek Block       | CTRL S       | ^s             |

| Enquiry          | CTRL E       | ^E             |

| Verify Block     | CTRL V       | <b>^</b> v     |

| Write Buffer     | CTRL B       | <b>^</b> B     |

| Access Buffer    | CTRL A       | ^A             |

| Fill Buffer      | CTRL F       | ^F             |

| Put in Buffer    | CTRL P       | ^p             |

| List Directory   | CTRL D       | ^D             |

| Open File        | CTRL O       | • <b>^</b> 0   |

| Kill File        | CTRL K       | ^K             |

| Rewind Drive     | CTRL Z       | 2              |

| Select Track     | CTRL T       | *т             |

| Initialize Track | CTRL I       | I              |

| Cancel Command   | CTRL X       | <b>^</b> X     |

TABLE 3-5. CTU COMMAND FUNCTIONS

HM-080-0019-01 POINT 4 Data Corporation

3-11

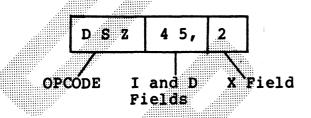

# 3.3.1.2 Command Pormat

All CTU commands are structured as follows:

COMMAND [BLOCK NO.], [ADD'L BLOCK COUNT] RETURN

NOTE

All fields enclosed by brackets are optional fields.

Field functions can be described as follows:

#### COMMAND

This is a one-character control code specifying the function to be performed. See Subsection 3.3.1.1 for a complete listing of control codes and their functions.

#### [BLOCK NO.]

This is an optional DECIMAL block address specification. Zero (0) is the first block address. The maximum block address depends upon tape length (typically 999).

NOTE

CTU blocks contain only 128 words; IRIS blocks contain 256 words.

#### [ADDITIONAL BLOCK COUNT]

This is an optional DECIMAL field which specifies the number of blocks to be operated upon in addition to the block specified in the [BLOCK NO.] field. A specification of zero (0) for this field instructs the CTU to operate only on the block specified in the [BLOCK NO.] field. The maximum count is 255.

#### RETURN

An ASCII carriage return character is the execute instruction for the CTU. If the CTU receives a CTRL X before a RETURN, the CTU cancels (does not execute) the preceding command string specified. A new command can follow the RETURN.

## 3.3.1.3 CTU Error Conditions

The CTU will report error conditions by presentation of an error code. An error condition is given in the following format:

BELL, Error Code, BELL, RETURN, Line Feed

The error codes and the errors they represent are shown in Table 3-6.

## TABLE 3-6. CTU ERROR CODES

Error

R

?

F

## Description

A write operation was attempted on a write protected tape.

Tape motion failure. This error occurs either as a result of a jam or mechanical malfunction, or as a result of incorrect tape positioning due to operator handling. In case of incorrect tape positioning, the CTU does not know the tape location and thus runs into the stops.

Read error. The operator should retry the command. An excessive number of read errors usually indicates noise interference, faulty system ground, a defective tape or a CTU hardware malfunction.

U Unknown name. An attempt was made to delete a name not found in the directory.

Syntax error in command string.

Track Directory is full (126) names. An old name must be killed before a new name may be entered.

HM-080-0019-01 POINT 4 Data Corporation OPERATING PROCEDURES MARK III User Manual

# 3.3.2 CTU COMMANDS IN MANIP

To enter CTU mode from MANIP use MANIP command R to read the first three blocks from the CTU tape.

MANIP allows reading from CTU into RAM (CPU main memory), but does not allow writing onto tape. To write to the CTU, get a cassette which contains DBUG, read it into memory by means of MANIP, then Jump into DBUG and use its CTU write capabilities (see Section 3.3.3).

All MANIP commands consist of a control character (CTRL and an ASCII character), followed optionally by one or more parameters, and terminated by a RETURN. The only exception is CTRL X which cancels any partially entered command immediately. Data is stored on tape in blocks of 256 bytes (128 words) each. Table 3-7 lists the CTU commands used in MANIP. All numeric parameters (x, y below) are in DECIMAL, origin 0.

| Т                    | ABLE 3-7. CTU COMMANDS IN MANIP                                            |

|----------------------|----------------------------------------------------------------------------|

| Control<br>Character | Description                                                                |

| CTRL D               | List directory (index) from tape, if tape is so formatted.                 |

| CTRL E               | Enquire (error status).                                                    |

| CTRL Ofile           | Open the named file, if it is in the directory.                            |

| CTRL R               | Read the open file from tape into memory.                                  |

| CTRL Rx,y            | Read from tape into memory; read y+1 blocks starting at block x.           |

| CTRL Sx              | Seek to block x on tape. CTRL S999 will wind the tape all the way forward. |

| CTRL In              | Select track n (0 to 1).                                                   |

| CTRL X               | Cancel partially entered command.                                          |

| CTRL Z               | Rewind tape to starting position.                                          |

ESC exits CTU mode and reverts to normal MANIP commands, but does not cancel any partial command that may already have been transmitted to the CTU. Use CTRL X to cancel a partial command.

The Read command transfers data into memory starting at address 0. To start the transfer at some other address, precede the CTU command with:

Memory address (octal), colon, RETURN

MANIP will then display the content of the chosen location, followed by a colon. This allows examination of the word before starting the tape transfer. Then type the CTRL R, followed by its parameters (if any) and a RETURN.

## NOTE

HM-080-0019-01 POINT 4 Data Corporation

3-15

### 3.3.3 CTU COMMANDS IN DBUG

DBUG is a position-independent debug package of the IRIS Operating System. When using the Virtual Control Panel on the POINT 4 Computer it is necessary to use DBUG commands to write to the CTU. The write procedure from MANIP requires a cassette containing DBUG which must be read into memory using MANIP. A jump into DBUG allows use of DBUG CTU commands to write to the CTU. CTU commands in DBUG may also be used in other CTU transfer procedures.

All CTU commands consist of a control character, followed optionally by one or more parameters, and terminated by a RETURN. The only exception is CTRL X which cancels any partially entered command immediately. Data is stored on tape in blocks of 256 bytes (128 words) each. Table 3-8 lists the CTU commands used in DBUG. All numeric parameters (x, y below) are in DECIMAL, origin 0.

| TABLE 3-                         | B. CTU COMMANDS IN DBUG                                                                                                                       |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Control Character/<br>Parameters | Description                                                                                                                                   |

| CTRL Ax,y                        | Access CTU buffer, i.e., transfer<br>buffer into memory. Transfers y<br>bytes, starting at byte x. Default<br>= 256 bytes starting at byte 0. |

| CTRL Bx                          | Write CTU buffer onto tape, at<br>block x.                                                                                                    |

| CTRL D                           | List directory (index) from tape,<br>if tape is so formatted.                                                                                 |

| CTRL E                           | Enquire (error status).                                                                                                                       |

| CTRL F                           | Fill CTU buffer from memory (128<br>words).                                                                                                   |

| CTRL IX                          | Initialize (format) <b>sel</b> ected track<br>to x+l blocks of 128 words each.<br>Maximum = 1999 for 1000 blocks.                             |

| CTRL Kfile                       | Kill the named file, i.e., erase<br>its name from the directory.                                                                              |

| CTRL Ofile                       | Open the named file, if it is in the directory.                                                                                               |

| HM-080 | -0 | 01 | 9-0 | 1           |

|--------|----|----|-----|-------------|

| POINT  | 4  | Da | ta  | Corporation |

3 - 16

| TABLE 3-8. CT                    | U COMMANDS IN DBUG (Cont)                                                                                                                 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Control Character/<br>Parameters | Description                                                                                                                               |

| CTRL Ofile,x,y                   | Create a directory entry for the<br>named file (max. 5 char.), starting<br>at block x and containing y+1<br>blocks of 128 words each.     |

| CTRL Px,y                        | Put into CTU buffer from memory,<br>transferring y bytes beginning at<br>byte x in the buffer. Default =<br>256 bytes starting at byte 0. |

| CTRL R                           | Read the open file from tape into memory.                                                                                                 |

| CTRL Rx,y                        | Read from tape into memory; read<br>y+l blocks starting at block x.                                                                       |

| CTRL Sx                          | Seek to block x on tape.                                                                                                                  |

| CTRL In                          | Select track n (0 or 1).                                                                                                                  |

| CTRL V                           | Verify; i.e., read from tape into<br>CTU buffer, checking checksum.                                                                       |

| CTRL W                           | Write from memory onto tape into<br>the open file, if any.                                                                                |

| CTRL Wx,y                        | Write from memory onto tape,<br>writing y+1 blocks starting at<br>block x.                                                                |

| CTRL X                           | Cancel partially entered command.                                                                                                         |

| CTRL Z                           | Rewind tape to starting position.                                                                                                         |

# NOTE

ESC exits CTU mode and reverts to normal DBUG commands, but does not cancel any partial command that may already have been transmitted to the CTU. Use CTRL X to cancel that.

3-17

All commands that transfer data into or out of main memory default to an intial address of 0. To start the transfer at some other address, precede the CTU command with:

Memory address (octal), colon, RETURN

DBUG will then display the content of the chosen location, followed by a colon. This allows examination of the word before starting the tape transfer. Then type the CTU control character (e.g., CTRL R or CTRL W), followed by its parameters and a RETURN.

Table 3-9 is a guick-reference guide to the commands used for data transfer from a source to a destination.

|        | Destination | Command                                                      |

|--------|-------------|--------------------------------------------------------------|

| Tape   | Memory      | ^R                                                           |

|        | Таре        | Ŵ                                                            |

| Tape   |             | °v                                                           |

| Buffer | Таре        | ˆB                                                           |

| Buffer | Memory      | ^A                                                           |

| Memory | Buffer      | <b>^F complete buffer</b><br><b>^P selected byte(s) only</b> |

SUMMARY AND OVERVIEW OF DATA TRANSFER COMMANDS TABLE 3-9.

#### 3.4 POWERING UP THE SYSTEM

The following steps should be followed when first applying power to the POINT 4 MARK III power supply and processor:

- 1. Turn the power-control switch on the front Mini-Panel to ON.

- 2. The carry light comes on for approximately 1.5 seconds, goes off for .5 seconds, comes on again and remains illuminated.

- 3. The Master CRT displays OK, indicating that the system has run a successful CPU self-test program.

- 4. If the disc drive is in a Ready state, the CRT displays PRESS RETURN. Upon entry of a RETURN, the system loads the program from the disc drive.

- 5. If the disc drive is not in a Ready state, press the RESET button on the Mini-Panel, which accesses the MANIP program. The CRT displays the contents of the program counter annd accumulators. Press P on the CRT keyboard, followed by a RETURN.

- 6. The CRT displays PRESS RETURN. Upon entry of a RETURN the system loads the program from the disc drive.

## 3.5 DIAGNOSTIC CHECKS

### 3.5.1 DIAGNOSTIC CAPABILITIES

The POINT 4 MARK III has a comprehensive built-in diagnostic program, contained in a PROM (Programmable Read-Only Memory).

The Self-Test diagnostic contains the following tests:

- 1. Compare Instruction Test

- 2. ALU and Data Bus Test

- 3. ALU Source Operand Test

- 4. Exhaustive ALU Instruction Test

- 5. Page 0 and Base 3 Addressing Modes Test

- 6. Relative, Base 2, and Indirect Addressing Modes Test

- 7. Limited I/O Instruction Test

- 8. Worst-Case Memory Test of all Memory Locations

# 3.5.2 SELF-TEST OPERATING PROCEDURES

General procedures for initiating the POINT 4 MARK III Self-Test follow. For details on tests executed, expected results, and error interpretation, see the POINT 4 MARK III Diagnostics Manual.

A T (Test) Command, followed by a RETURN initiates the MARK III Self-Test program. Successful completion results in OK displayed on the Master Terminal. Thereafter, each time the Self-Test repeats, an OK is displayed. The Self-Test program continues until RESET is pressed.

#### 3.5.3 SELF-TEST ERRORS

A Self-Test error is indicated by a continuously flashing carry light. Refer to the POINT 4 MARK III Diagnostic Manual for detailed information on diagnostic programs, program listings, and error interpretation.

## Section 4

## INPUT/OUTPUT INTERPACES

#### 4.1 INPUT/OUTPUT BUS INTERFACE SIGNALS

Input/Output Bus signals connect the processor logic to peripheral device logic. The logic for programmed I/O transfers and data channel transfers forms the interface between the processor Main Data Bus and the peripheral device controller logic. Logic to implement I/O transfer instructions is present in all device controllers. Data channel transfer logic is present only in those controllers that control devices using the data channel. Device-end control logic for these functions may vary widely, depending on the requirements of the particular device. This subsection describes the POINT 4 MARK III I/O bus and control signals, including any special signals used for disc or tape controller interface.

## 4.1.1 INPUT/OUTPUT INTERFACE SIGNALS

Signals on the Input/Output Bus can be grouped into the following signal classifications:

- a. Bidirectional Data Bus (16 lines): Used for transfer of all data and address words between the CPU and a peripheral device, for both programmed I/O and data channel transfers.

- b. Device Codes (6 lines): Codes used to designate the peripheral device involved in an input/output instruction.

- c. Device Control Signals (2 lines): These signals are generated by the CPU in response to input/output instructions, and are used to initialize and control I/O devices.

- d. Interrupt Input Signals (3 lines): Signals used to control which controller (multiplexer disc or tape) will be serviced.

- e. Disc Status Flags (5 lines): Signals used to carry disc status information to the processor.

Figure 4-1 is a diagram of I/O signals across the I/O Bus. Table 4-1 divides these signals by signal classifications, designates the signal name and defines each signal function.

HM-080-0019-01 POINT 4 Data Corporation

HM-080-0019-01 POINT 4 Data Corporation INPUT/OUTPUT INTERFACES MARK III User Manual

# TABLE 4-1. INPUT/OUTPUT SIGNALS BY CLASSIFICATION

| Signal<br>Group              | Signal*               | Direction          | Description                                                                                                                                                          |

|------------------------------|-----------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data<br>Bus                  | DB00<br>to<br>DB015   | Bidirec-<br>tional | All data and addresses are<br>supplied to and from the device<br>via these lines. DB00+ is the<br>MSB.                                                               |

| Device                       | DSO-<br>to<br>DS5-    | From CPU           | The CPU places the device code<br>(bits 10-15 of the instruction<br>word) on these lines during the<br>execution of an input/output<br>instruction. DSO- is the MSB. |

| Device<br>Control<br>Signals | IOBRST-               | From CPU           | Input/Output Reset. Generated<br>when APL is pressed on the<br>Mini-panel, when an IOBRST<br>instruction is being executed,<br>and during power turn-on.             |

| I                            | IOBPLS-               | From CPU           | Generated when CTRL field of an<br>input/output transfer<br>instruction contains code 11.<br>The effect, if any, depends on<br>the device.                           |

|                              | BW-/R                 | From CPU           | Set by firmware to control the<br>direction of data and control<br>transfer based on the<br>instruction issued for that<br>operation.                                |

| Inter-<br>rupt<br>Input      | ATNMUX-               | From Device        | Used by multiplexer to signal<br>its need for interrupt<br>servicing.                                                                                                |

|                              | ATNDISC-              | From Device        | Used by the disc controller to<br>signal its need for interrupt<br>servicing.                                                                                        |

|                              | ATNTPE-               | From Device        | Used by the disc controller to<br>signal its need for interrupt<br>servicing.                                                                                        |

| Disc<br>Status<br>Flags      | FLAGO<br>to<br>FLAG4  | From Device        | Used by firmware to transfer<br>status information.                                                                                                                  |

|                              | nal names<br>ve high. | ending with        | "-" are active low. All others                                                                                                                                       |

HM-080-0019-01 POINT 4 Data Corporation 4-3

# 4.1.2 BACKPLANE PIN SIGNAL CONNECTORS

All signal connections between the processor and each controller take place via two 100-pin backplane connectors. Figure 4-2 shows the connector pin layout for all I/O signals. The labelled pins refer to the I/O control signals, data transfer signals and the power lines used by peripheral controllers.

|   | Bottom   | A               |            | Тор              | Bottom         |             | B        | Тор            |

|---|----------|-----------------|------------|------------------|----------------|-------------|----------|----------------|

| _ | GND      | 1               | 2          | GND              | GND            | 1           | 2        | GND            |

|   | GND      | 3               | 4          | GND              | GND            | 3           | 4        | GND            |

|   | +5V      | 5<br>7          | 6          | +5V              | +5V            | 3<br>5<br>7 | 6        | +5V            |

|   | +5V      | 7               | 8          | +5V              | +5V            |             | 8        | +5V            |

|   | DS2-     | 9               | 10         | DS1-             | DS2-           | 9           | 10       | DS1-           |

|   | DS0-     | 11              | 12         | DS5-             | DS0-           | 11          | 12       | DS5-           |

|   | DSY-     | 13              | 14         | DS3-             | DSY-           | 13          | 14       | DS3-           |

|   | BS-/R+   |                 | 16         | DB15+            | BS-/R+         | 15          | 16       | DB15+          |

|   | DB14+    | 17              | 18         | DB13+            | DB14+          | 17          | 18       | DB13+          |

|   | DB12+    | 19              | 20         | DB11+            | DB12+          | 19<br>21    | 20<br>22 | DB11+<br>DB09+ |

|   | DB10+    | 21              | 22         | DB09+            | DB10+<br>DB08+ | 23          | 24       | DB09+<br>DB07+ |

|   | DB08+    |                 | 24         | DB07+            | DB06+          | 25          | 26       | DB05+          |

|   | DB06+    | 25              | 26         | DB05+            | DB04+          | 25          | 28       | DB03+          |

|   | DB04+    | 27              | 28         | DB03+            | DB04+          | 29          | 30       | DB03+          |

|   | DB02+    | 29              | 30         | DB01+            | DB02+          | 31          | 32       | GND            |

|   | DB00+    | 31              | 32         | GND<br>IOBRST-   | GND            | 33          | 34       | IOBRST-        |

|   | GND      | 33              | 34         |                  | GND            | 35          | 36       | GND            |

|   | GND      | 35              | 36<br>38   | GND              | IOBPLS-        | 37          | 38       | GND            |

|   | IOBPLS-  | 37              |            | GND<br>BT NCA-   | GND            | 39          | 40       | FLAG4-         |

|   | GND      | 39              | 40         | PLAG4-<br>PLAG2- | FLAG3-         | 41          | 42       | FLAG2-         |

|   | FLAG3-   | 41              | 42         | PLAGO-           | PLAG1-         | 43          | 44       | FLAG0-         |

|   | PLAG1-   | 43<br>45        | 46         | ATNMUX-          | ATNDISC-       | 45          | 46       | ATNMUX-        |

|   | ATNDISC- | 47              | 48         | GND              | ATNTPL         | 47          | 48       | GND            |