POINT 4TM

MARK 3

COMPUTER

SYSTEM MANUAL

NOT UPTO DATE

# POINT 4 DATA CORPORATION

2569 McCabe Way / Irvine, California 92714

POINT 4<sup>™</sup>

MARK 3

COMPUTER

SYSTEM MANUAL

#### NOTICE

Every attempt has been made to make this reference manual complete, accurate and up-to-date. However, all information herein is subject to change due to updates. All inquiries concerning this manual should be directed to POINT 4 Data Corporation.

Copyright © 1981, 1982 by POINT 4 Data Corporation (formerly Educational Data Systems, Inc). Printed in the United States of America. All rights reserved. No part of this work covered by the copyrights hereon may be reproduced or copied in any form or by any means--graphic, electronic, or mechanical, including photocopying, recording, taping, or information and retrieval systems--without the written permission of:

> POINT 4 Data Corporation 2569 McCabe Way Irvine, CA 92614 (714) 754-4114

## **REVISION RECORD**

PUBLICATION NUMBER: HM-081-0019

| Revision | Description                                                                                                                         | <u>Date</u> |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 01       | Draft Version to coincide with delivery of first MARK 3                                                                             | 05/15/81    |

| A        | Complete update incorporating corrections and new material; PIB interface is now covered in the MARK 3 Peripherals Interface Manual | 06/09/82    |

## LIST OF EFFECTIVE PAGES

Changes, additions, and deletions to information in this manual are indicated by vertical bars in the margins or by a dot near the page number if the entire page is affected. A vertical bar by the page number indicates pagination rather than content has changed.

| <u>Page</u>    | Rev | <u>Page</u> | Rev | Page | Rev |

|----------------|-----|-------------|-----|------|-----|

|                |     |             |     |      |     |

| Cover          | _   |             |     |      |     |

| Title          | -   |             |     |      |     |

| ii thru xi     | A   |             |     |      |     |

| 1-1 thru 1-12  | A   |             |     |      |     |

| 2-1 thru 2-23  | A   |             |     |      |     |

| 3-1 thru 3-20  | A   |             |     |      |     |

| 4-1 thru 4-5   | A   |             |     |      |     |

| 5-1 thru 5-34  | A   |             |     |      |     |

| 6-1 thru 6-5   | A   |             |     |      |     |

| Appendix Title | _   |             |     |      |     |

| A-1            | A   |             |     |      |     |

| B-1            | A   |             |     |      |     |

| C-1            | A   |             |     |      |     |

| D-1            | A   |             |     |      |     |

| E-1 thru E-10  | A   |             |     |      |     |

| Comment Sheet  | A   |             |     |      |     |

| Mailer         | _   |             |     |      |     |

| Back Cover     | -   |             |     |      |     |

## **PREFACE**

This manual describes the POINT 4 MARK 3 Computer System, a 16-bit, general-purpose minicomputer with instruction set.

The introduction describes standard features of the POINT 4 MARK 3 and includes detailed information on equipment and performance characteristics, and system architecture. Optional features are described in a separate section.

The MARK 3 Peripheral Interface Board (PIB) with built-in multiplexer, printer, disc and tape interfaces is described in a separate document (see related manuals).

Step-by-step directions for installation, upgrade, and detailed operating procedures are provided. Sections describing the input/output interface and the standard instruction set are included.

The appendices provide cabling information, summary information of POINT 4 MARK 3 commands and instructions, and programming examples.

Related manuals include:

Title Pub. Number

POINT 4 MARK 3 Peripherals Interface

Manual HM-081-0026

POINT 4 MARK 3 Diagnostics Manual

water he

## **CONTENTS**

| Section                                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                         |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 1                                                                                                                    | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                          |

| 1.1<br>1.1.1<br>1.2<br>1.2.1<br>1.2.2<br>1.3<br>1.3.1.1<br>1.3.1.2<br>1.3.1.3<br>1.3.1.4<br>1.3.1.5                  | GENERAL DESCRIPTION Features EQUIPMENT CHARACTERISTICS Performance Characteristics Equipment Specifications SYSTEM ARCHITECTURE System Functional Units Central Processor and Memory Board Peripheral Interface Board Power Supply Board Chassis and Front Panel Mini-Panel                                                                                                                                                                               | 1-1<br>1-2<br>1-3<br>1-3<br>1-4<br>1-5<br>1-7<br>1-7<br>1-10<br>1-11<br>1-12 |

| 2                                                                                                                    | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-1                                                                          |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.2<br>2.2.1<br>2.2.2<br>2.3.1<br>2.3.2<br>2.4.1<br>2.4.2<br>2.4.3<br>2.5<br>2.5.1 | ENVIRONMENTAL REQUIREMENTS Power Requirements Temperature Requirements Enclosure Requirements UNPACKING INSTRUCTIONS Unpacking The Cartons Container Contents MOUNTING INSTRUCTIONS Front Panel Chassis MARK 3 INSTALLATION PROCEDURE Checking the Boards Connecting MUX Cables Powering Up the MARK 3 System UPGRADING AN EXISTING MARK 3 Upgrading a MARK 3 to 128KB Memory Memory Expansion Requirements Memory Expansion Board Installation Procedure | 2-1 2-1 2-1 2-1 2-1 2-2 2-2 2-2 2-4 2-4 2-4 2-6 2-6 2-9 2-11 2-13 2-13 2-13  |

| 2.5.2<br>2.5.2.1<br>2.5.2.2                                                                                          | Upgrading MARK 3 to Seven Ports MARK 3 Port Expansion Requirements Port Expansion Board Installation Procedure                                                                                                                                                                                                                                                                                                                                            | 2-17<br>2-17<br>2-18                                                         |

| 2.6                                                                                                                  | PIB CABLING                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-18                                                                         |

| 3                  | OPERATING PROCEDURES                               | 3-1         |

|--------------------|----------------------------------------------------|-------------|

| 3.1<br>3.2         | INTRODUCTION MINI-PANEL                            | 3-1<br>3-1  |

| 3.2.1              | Power Controls and Indicators                      | <b>.</b>    |

|                    | (Power Switch/Pwr OK Light)                        | 3-3         |

| 3.2.2              | Processor Operation Monitoring (Carry Light)       | 3-4         |

| 3.2.3              | Program Execution Control (Reset Switch)           | 3-4         |

| 3.2.4              | Battery Monitoring Indicators (Btry OK Light)      | 3-4         |

| 3.3                | VIRTUAL CONTROL PANEL                              | 3-5         |

| 3.3.1              | MANIP Program                                      | 3-5         |

| 3.3.2<br>3.4       | MANIP Command Descriptions PROCESSOR/CTU INTERFACE | 3-7<br>3-10 |

| 3.4.1              | CTU Commands                                       | 3-10        |

| 3.4.1.1            | Command Functions                                  | 3-11        |

| 3.4.1.2            |                                                    | 3-12        |

| 3.4.1.3            |                                                    | 3-13        |

| 3.4.2              | CTU Commands Enabled in MANIP                      | 3-14        |

| 3.4.3              | CTU Commands Enabled in DBUG                       | 3-16        |

| 3.4.4              | CTU Operating Procedures                           | 3-19        |

| 3.5                | DIAGNOSTIC CHECKS                                  | 3-20        |

| 3.5.1              | Diagnostic Capabilities                            | 3-20        |

|                    | Self-Test Operating Procedures                     | 3-20        |

| 3.5.3              | Self-Test Errors                                   | 3-20        |

|                    | TUDUM (OUMDUM TUMEDD) ODG                          | 4 1         |

| 4                  | INPUT/OUTPUT INTERFACES                            | 4-1         |

| 4.1                | INPUT/OUTPUT BUS                                   | 4-1         |

| 4.1.1              | Input/Output Interface Signals                     | 4-1         |

| 4.1.2              | Backplane Pin Signal Connectors                    | 4-4         |

|                    |                                                    |             |

| 5                  | STANDARD INSTRUCTION SET                           | 5-1         |

|                    |                                                    | _           |

| 5.1                | INTRODUCTION                                       | 5-1         |

| 5.2                | OCTAL REPRESENTATION AND TWO'S                     |             |

|                    | COMPLEMENT NOTATION                                | 5-1         |

| 5.3                | INSTRUCTION TYPES                                  | 5-3         |

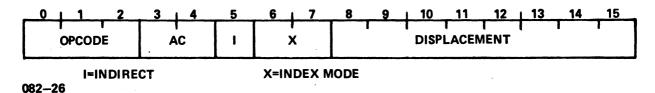

| 5.4                | MEMORY REFERENCE INSTRUCTIONS                      | 5-5<br>5-5  |

| 5.4.1              | Memory Addressing                                  | 5-3<br>5-7  |

| 5.4.1.1<br>5.4.1.2 | Indexing Mode<br>Indirect Addressing Operations    | 5-8         |

| 5.4.2              | Types of Memory Reference Instructions             | 5-8         |

| 5.4.2.1            | Move Data Instructions                             | 5-8         |

| 5.4.2.2            | Jump and Modify Memory Instructions                | 5-9         |

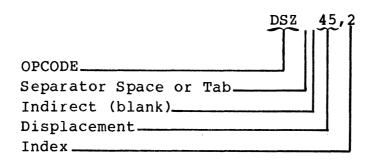

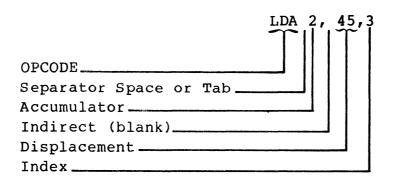

| 5.4.2.3            | Assembler Language Conventions and                 |             |

| <del></del>        | Addressing Examples                                | 5-10        |

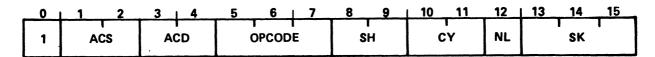

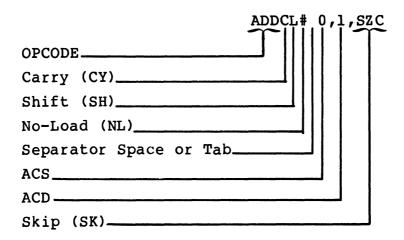

| 5.5         | ARITHMETIC AND LOGICAL INSTRUCTION GROUP | 2010<br>2010<br>2010<br>2010             | 5-12  |

|-------------|------------------------------------------|------------------------------------------|-------|

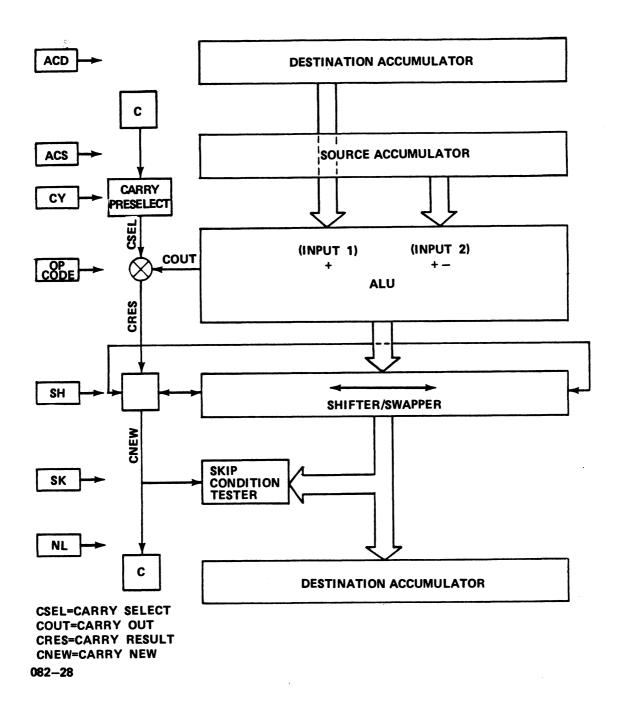

| 5.5.1       | Arithmetic and Logical Processing        |                                          | 5-12  |

| 5.5.1.1     | Arithmetic/Logical Operations            |                                          | 5-14  |

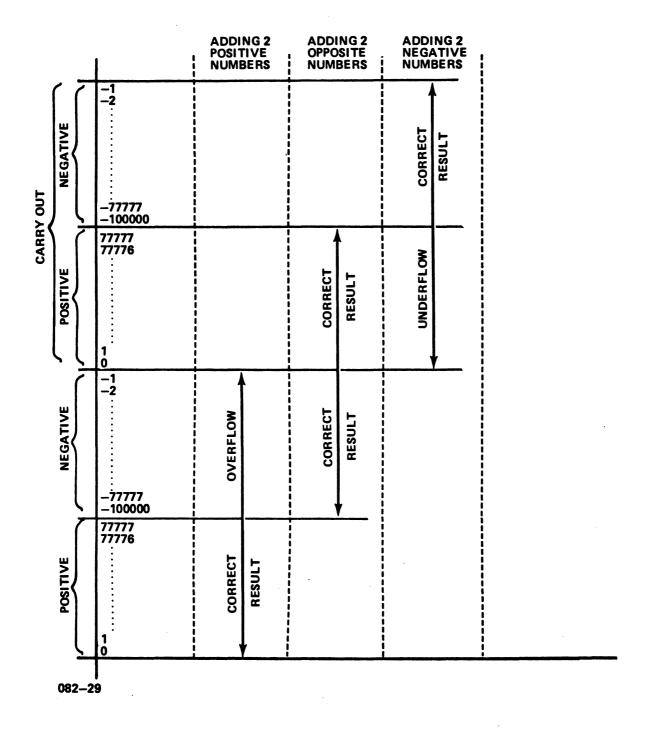

| 5.5.1.2     | Overflow and Carry-Out Operations        |                                          | 5-15  |

| 5.5.2       | Arithmetic/Logic Functions               | e 2                                      | 5-18  |

| 5.5.3       | Secondary Functions                      | t.<br>L. J.                              | 5-19  |

| 5.5.3.1     | Shift Field (SH)                         |                                          | 5-19  |

| 5.5.3.2     | Carry Control Field (CY)                 |                                          | 5-20  |

| 5.5.3.3     | No-Load Field (NL)                       |                                          | 5-20  |

| 5.5.3.4     | Skip Control Field (SK)                  |                                          | 5-21  |

| 5.5.4       | Assembler Language Conventions           |                                          |       |

|             | and Examples                             |                                          | 5-22  |

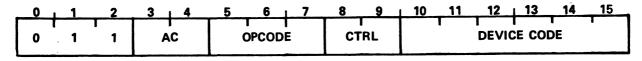

| 5 <b>.6</b> | INPUT/OUTPUT INSTRUCTION GROUP           |                                          | 5-24  |

| 5.6.1       | Programmed I/O Instructions              |                                          | 5-24  |

| 5.6.1.1     | I/O Transfer Instructions                | *.                                       | 5-25  |

| 5.6.1.2     | Assembler Language Conventions           |                                          |       |

| 3.0.1.2     | and Examples                             |                                          | 5-26  |

| 5.6.2       | Special Code 77 (CPU) Instructions       |                                          | 5-28  |

| 5.6.2.1     | Special Mnemonics for CPU Instructions   |                                          | 5-28  |

| 5.6.2.2     | Control Field Uses                       |                                          | 5-30  |

|             |                                          |                                          | 5-32  |

| 5.6.2.3     | Skip Instructions                        |                                          | 3-32  |

| 5.6.2.4     | Assembler Language Conventions           |                                          | E 22  |

|             | and Examples                             |                                          | 5-32  |

| 5.7         | INSTRUCTION EXECUTION TIMES              |                                          | 5-33  |

| e           | ODMIONAL REAMIDEC                        |                                          | 6-1   |

| 6           | OPTIONAL FEATURES                        |                                          | 0 - T |

| <i>c</i> 1  | INTRODUCTION                             | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 | 6-1   |

| 6.1         |                                          |                                          |       |

| 6.2         | 64K-BYTE MEMORY EXPANSION BOARD          |                                          | 6-2   |

| 6.3         | PORT EXPANSION BOARD                     | 4                                        | 6-4   |

## **APPENDICES**

| A | Cable Length Considerations                | A-1 |

|---|--------------------------------------------|-----|

| В | ASCII Code Chart                           | B-1 |

| С | Von Neumann Map of POINT 4 MARK 3 Commands | C-1 |

| D | POINT 4 MARK 3 Instruction Chart           | D-1 |

| E | Programming Examples                       | E-1 |

## **FIGURES**

| Number | Title                                                                      | Page |

|--------|----------------------------------------------------------------------------|------|

| 1-1    | The POINT 4 MARK 3 Computer                                                | 1-1  |

| 1-2    | Typical POINT 4 MARK 3 Configuration                                       | 1-6  |

| 1-3    | POINT 4 MARK 3 Computer System Block Diagram                               | 1-8  |

| 1-4    | POINT 4 MARK 3 CPU/Memory Block Diagram                                    | 1-9  |

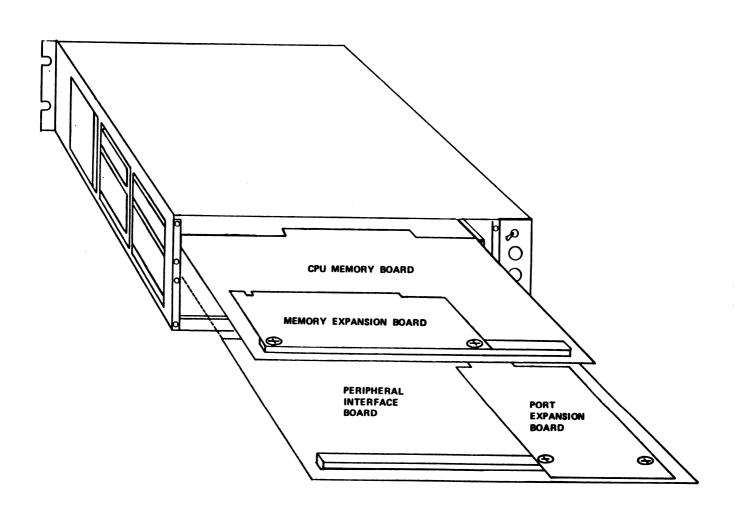

| 2-1    | POINT 4 MARK 3 Processor Chassis Packaging                                 | 2-3  |

| 2-2    | POINT 4 MARK 3 Chassis Mounting Slots                                      | 2-5  |

| 2-3    | POINT 4 MARK 3 Chassis with Rear Panel                                     |      |

|        | Open Showing Mounting Slots                                                | 2-7  |

| 2-4    | POINT 4 MARK 3 Board Configuration                                         | 2-8  |

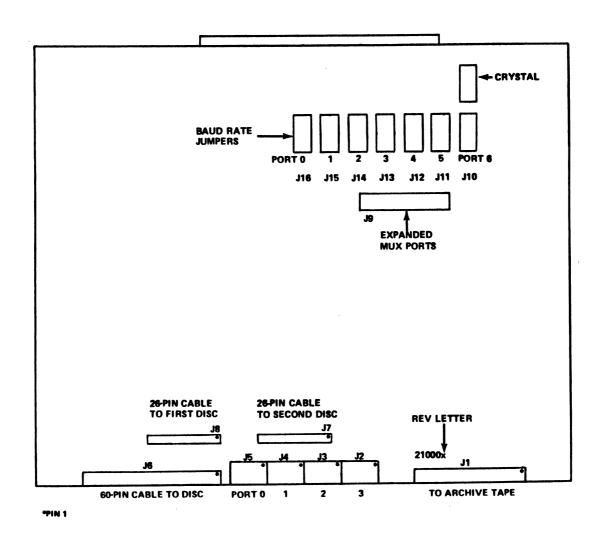

| 2-5    | POINT 4 MARK 3 Peripheral Interface Board                                  | 0.10 |

|        | Connector Positions                                                        | 2-10 |

| 2-6    | POINT 4 MARK 3 CPU Board                                                   | 2-14 |

| 2-7    | Installation of MARK 3 Memory Expansion                                    | 2-16 |

| 2 0    | and Port Expansion Boards                                                  | 2-10 |

| 2-8    | MARK 3 Asynchronous CRT/Printer Cable<br>Ports 0-3, PIB Revisions A thru C | 2-21 |

| 2-9    | MARK 3 Asynchronous CRT/Printer Cable                                      | 2-21 |

| 2-3    | Ports 0-3, PIB Revision D (and later)                                      |      |

|        | Ports 4-6, All Port Expansion Boards                                       | 2-22 |

| 2-10   | MARK 3 Asynchronous Modem Cable                                            | L LL |

| 2-10   | Ports 0-3, PIB Revision D (and later)                                      |      |

|        | Ports 4-6, All Port Expansion Boards                                       | 2-23 |

| 3-1    | POINT 4 MARK 3 Mini-Panel                                                  | 3-2  |

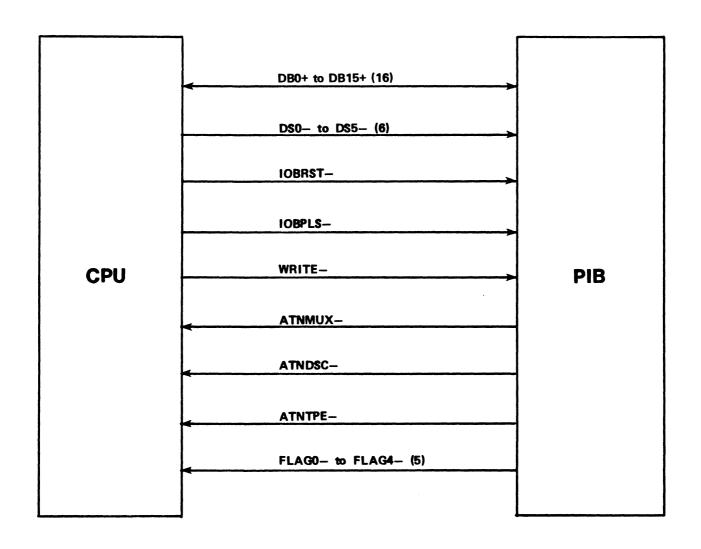

| 4-1    | Input/Output Signals                                                       | 4-2  |

| 4-2    | Backplane I/O Signals                                                      | 4-5  |

| 4-2    | •                                                                          |      |

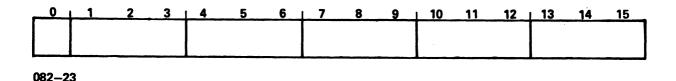

| 5-1    | POINT 4 MARK 3 16-bit Binary Word Format                                   | 5-1  |

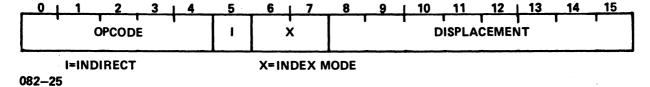

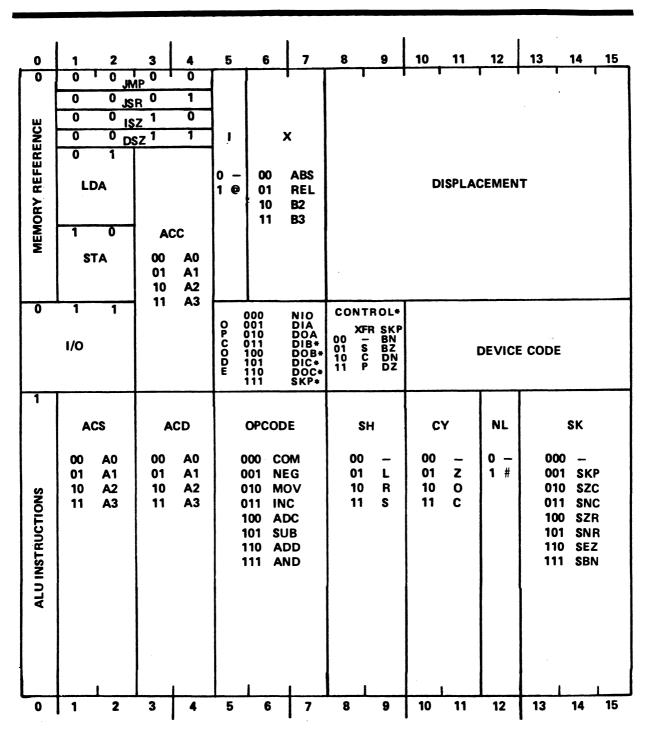

| 5-2    | POINT 4 MARK 3 Instruction Format Summary                                  | 5-4  |

| 5-3    | Jump and Modify Memory Instruction Binary Word Format                      | 5-5  |

| 5-4    | Move Data Instruction Binary Word Format                                   | 5-5  |

| 5-5    | Arithmetic/Logical Instruction Format                                      | 5-12 |

| 5-6    | Arithmetic/Logical Operations                                              | 5-13 |

| 5-7    | Overflow and Carry Operations Analysis                                     |      |

|        | for Signed Integers                                                        | 5-17 |

| 5-8    | Input/Output Instruction Format                                            | 5-24 |

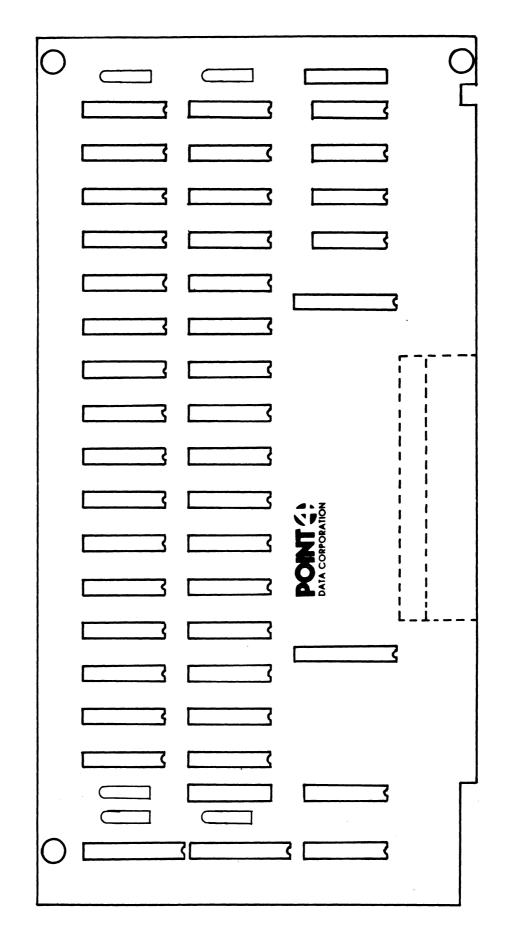

| 6-1    | POINT 4 MARK 3 64K-byte Memory Expansion Board                             | 6-3  |

| 6-2    | DOING A MADE 2 Dort Evnancion Roard                                        | 6-5  |

## **TABLES**

| Number | <u>Title</u>                        | <u>Page</u> |

|--------|-------------------------------------|-------------|

| 2-1    | MARK 3 Cable Usage                  | 2-20        |

| 3-1    | Power Control Switch Functions      | 3-3         |

| 3-2    | Power OK LED Interpretations        | 3-3         |

| 3-3    | Summary of MANIP Command Functions  | 3-6         |

| 3-4    | MANIP Commands                      | 3-7         |

| 3-5    | CTU Command Functions               | 3-11        |

| 3-6    | CTU Error Codes                     | 3-13        |

| 3-7    | CTU Commands in MANIP               | 3-15        |

| 3-8    | CTU Commands Enabled in DBUG        | 3-16        |

| 3-9    | Summary of Data Transfer Commands   | 3-18        |

| 4-1    | Input/Output Signals                | 4-3         |

| 5-1    | Memory Reference Instructions       | 5-6         |

| 5-2    | Indexing Modes                      | 5-7         |

| 5-3    | Move Data Instructions              | 5-8         |

| 5-4    | Jump and Modify Memory Instructions | 5-9         |

| 5-5    | Assembler Language Conventions for  |             |

|        | Memory Reference Instructions       | 5-11        |

| 5-6    | Arithmetic/Logic Functions          | 5-18        |

| 5-7    | Shift Field Definitions             | 5-19        |

| 5-8    | Carry Control Field                 | 5-20        |

| 5-9    | Skip Control Field                  | 5-21        |

| 5-10   | Assembler Language Conventions for  |             |

|        | Arithmetic and Logical Instructions | 5-23        |

| 5-11   | I/O Transfer Instructions           | 5-25        |

| 5-12   | Assembler Language Conventions for  |             |

|        | Input/Output Transfer Instructions  | 5-27        |

| 5-13   | Special CPU I/O Instructions        | 5-29        |

| 5-14   | Control Field Definitions for I/O   |             |

|        | Instructions with Device Code 77    | 5-31        |

| 5-15   | I/O Skip Instructions               | 5-32        |

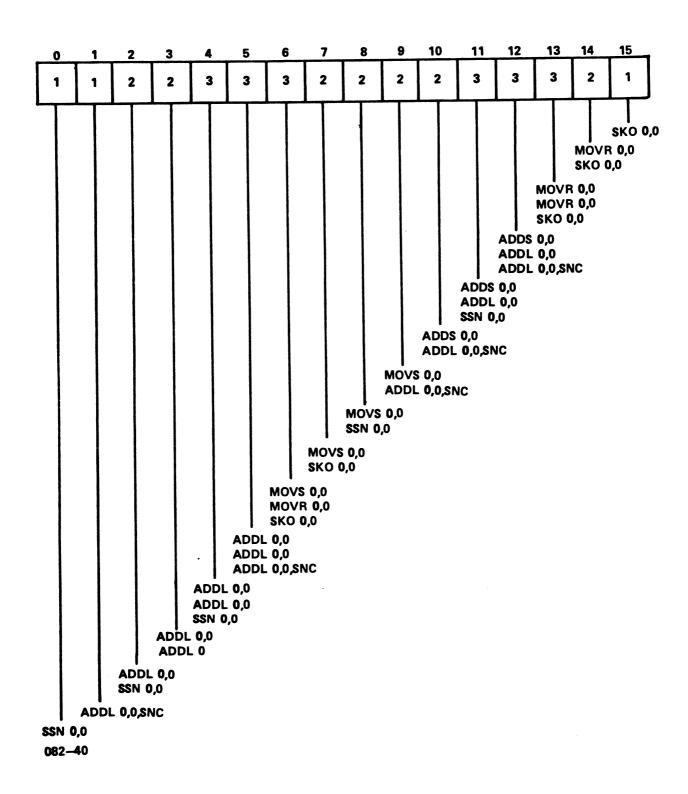

| 5-16   | Instruction Execution Times         | 5-34        |

|  |  | anning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|  |  | Learning Mark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|  |  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|  |  | and the second s |

|  |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Section 1 INTRODUCTION

## 1.1 GENERAL DESCRIPTION

The POINT 4 MARK 3 Computer\* is a 16-bit general-purpose minicomputer with a versatile instruction set. The POINT 4 MARK 3 employs a novel design architecture to achieve the simplicity and flexibility of a microprogrammed design with the speed of a hard-wired logic design. In addition the design allows direct addressing of up to 128K bytes of MOS random access These features make the POINT 4 MARK 3 Computer well suited to OEM applications in business data systems, and control systems. See Figure 1-1 for a photograph of the POINT 4 MARK 3 Computer.

Figure 1-1. POINT 4 MARK 3 Computer

<sup>\*</sup>Patent Pending

## 1.1.1 FEATURES

The POINT 4 MARK 3 Computer includes the following features:

- CPU and 64K bytes of RAM on the same board

- Peripheral Interface Board (PIB) with built-in multiplexer, printer, disc, and tape interfaces (see the separate MARK 3 Peripherals Interface Manual)

- Four asynchronous ports, baud-rate selectable to 9600 baud

- Up to two sector-mark signal-type SMD/CMD drives

- Up to four streamer tape drives

- Disc transfer rates to 1.25 megabytes per second

- Tape transfer rates to 90 kilobytes per second (at 90 inches per second)

- Virtual control panel

- Internal power supply for CPU and PIB boards

- Optional 64K-byte Memory Expansion Board for a total of 128K bytes

- Optional Port Expansion Board providing up to seven ports

## 1.2 EQUIPMENT CHARACTERISTICS

## 1.2.1 PERFORMANCE CHARACTERISTICS

16-bits Word Length:

General Purpose Accumulators:

Special Purpose Registers: 12

Memory Cycle Time: 600 nanoseconds

RAM Access Time: 200 nanoseconds

Microprogram Cycle Time: 200 nanoseconds

Memory: 64K bytes

DMA for Disc Controller

Input 1200 nanoseconds per word 1200 nanoseconds per word Output

DMA for Multiplexer Automatically vectored

byte access 10 microseconds per byte

DMA for Tape Transfer Rate approximately

5 microseconds per byte

Interrupt Response: 2000 nanoseconds

Backplane: 100-pin edge connector

## 1.2.2 EQUIPMENT SPECIFICATIONS

#### POWER SUPPLY

AC Voltages Required (jumper programmed): 117 VAC, +10%/-15%; 5 amps max; 47 to 63 Hz 234 VAC, +10%/-15%; 2.5 amps max; 47 to 63 Hz

DC Voltages Provided:

+5V @ 20 amps -5V @ .5 amps +12V @ 1.5 amps -12V @ .1 amps

Power Required: 180 watts maximum

Thermal Dissipation: Approximately 600 BTU/hour maximum

Maximum Inrush Current: 12 amps peak

#### OPERATING ENVIRONMENT

Ambient Temperature Range: 32-122°F (0-50°C) Relative Humidity: 10 to 90% noncondensing

#### **MECHANICAL**

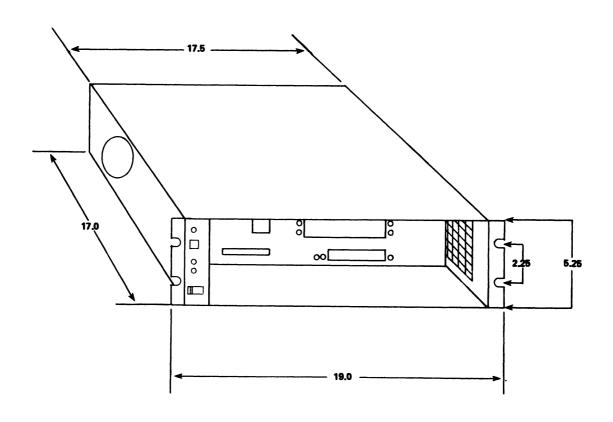

Processor Chassis Dimensions - 5.25 inches high (14 cm) 19.0 inches wide (48.3 cm) 17.5 inches deep (44.5 cm) Weight: 30 pounds (13.5 kilograms)

CPU/Memory PCB Dimensions: 14.5" x 12"  $(36.8 \text{ cm } \times 30.5 \text{ cm})$

Peripheral Interface Board Dimensions: 14.5" x 12"  $(36.8 \text{ cm } \times 30.5 \text{ cm})$

Power Supply Board Dimensions: 14.5" x 12"  $(36.8 \text{ cm } \times 30.5 \text{ cm})$

## 1.3 SYSTEM ARCHITECTURE

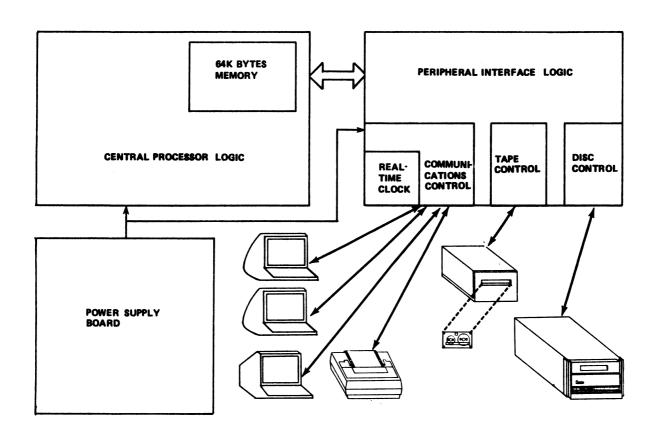

The POINT 4 MARK 3 architecture has been streamlined to create a system with a minimum of signal interfacing between boards and with a maximum speed of instruction execution. A combination of central processor logic and up to 64K bytes of RAM on a single circuit board eliminates time delays due to long memory access bus paths. The combination of all I/O control functions on the Peripheral Interface Board provides maximum efficiency and minimum backplane signal travel. An integrated power supply provides power for all POINT 4 MARK 3 functions. Figure 1-2 illustrates a typical configuration of a POINT 4 MARK 3 Computer System.

Figure 1-2. Typical POINT 4 MARK 3 Configuration

#### 1.3.1 SYSTEM FUNCTIONAL UNITS

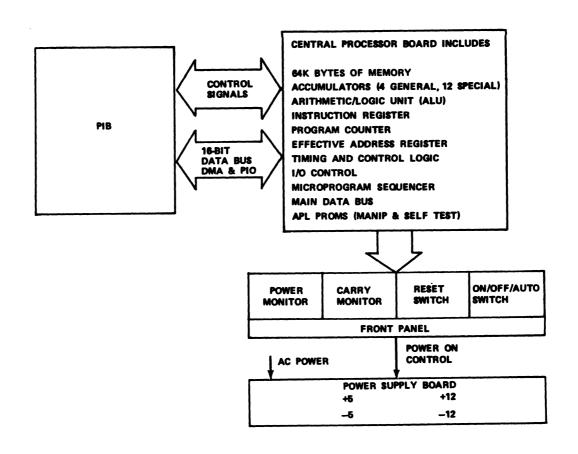

The POINT 4 MARK 3 is comprised of five functional units: the CPU and Memory Board, the Peripheral Interface Board, the Power Supply Board, the chassis and front panel, and the Mini-panel. Figure 1-3 is a block diagram of the basic units of the computer system showing the functions each unit performs.

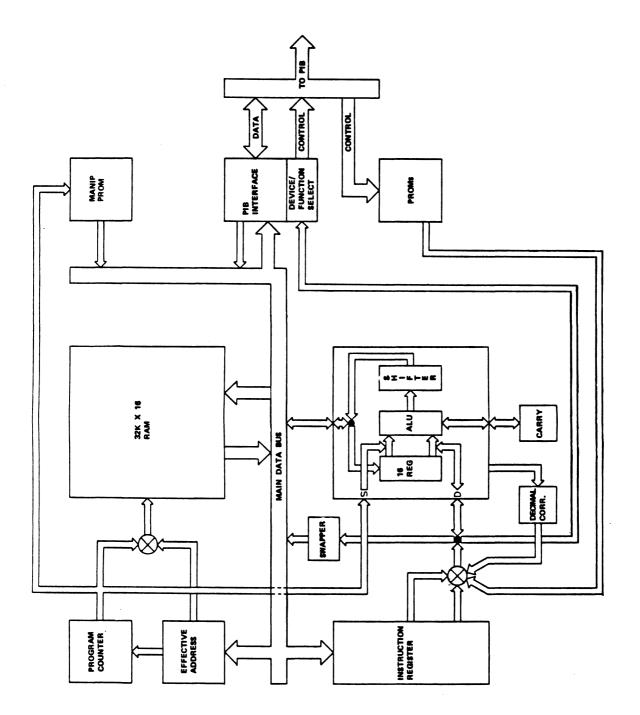

## 1.3.1.1 Central Processor and Memory Board

The Central Processor board contains all basic elements of the CPU:

- 2903 Microprocessor Bit Slice (4 bits wide) contains four general-purpose accumulators, plus 12 special-purpose registers and arithmetic/logic functions

- Microprogrammed Control Store (512 words x 64 bits) contains firmware to implement the software instruction set, as well as the disc controller, DMA multiplexer and tape controller functions for the PIB board

- Instruction Register

- Main Data Bus

- Program Counter

- Effective Address Register

- Timing Control

- Input/Output Control

- 64K Bytes of Random Access Memory (RAM)

- APL PROM contains a program to implement Virtual Control Panel Features, and the Self Test

Figure 1-4 is a block diagram of the POINT 4 MARK 3 System, showing logic to handle each of the above functions.

Figure 1-3. POINT 4 MARK 3 Computer System Block Diagram

Figure 1-4. POINT 4 MARK 3 CPU/Memory Block Diagram

## 1.3.1.2 Peripheral Interface Board

The Peripheral Interface Board contains all elements necessary for control of peripheral devices connected to the POINT 4 MARK 3. Functions included are:

#### GENERAL CONTROL FUNCTIONS

- Command Decoding

- Data Transmission/Reception

- Device Decoding

- Status Recording

- CRC Generation

#### MULTIPLEXER CONTROL FUNCTIONS

- Real-Time Clock

- Baud Rate Selection

- Data Synchronization & Format Manipulation

- Port Selection

### DISC CONTROL FUNCTIONS

- Disc Selection

- DMA Bus Control

- Word Count

- Tag Line Control

#### TAPE CONTROL FUNCTIONS

- Tape Drive Selection

- Read/Write Operations

- Tape Positioning

- Status Reporting

- Error Processing/Recovery

The Peripheral Interface Board is described in a separate manual which provides detail of all aspects of peripheral device control (see the MARK 3 Peripherals Interface Manual).

## 1.3.1.3 Power Supply Board

The power supply is packaged on a single board (14.5 inches wide, 12 inches deep, and 2 inches high) with protective cover. It plugs directly into the MARK 3 backplane. Input voltage requirements and power supply output voltages are:

## AC INPUT

Voltage:

117 VAC +10%/-15%

234 VAC +10%/-15% (jumper programmed)

Frequency:

47-63 Hz

#### DC OUTPUTS

Voltages:

+5 VDC @ 20 amps -5 VDC @ .5 amps +12 VDC @ 1.5 amps -12 VDC @ 0.1 amps

#### 1.3.1.4 Chassis and Front Panel

The POINT 4 MARK 3 chassis is designed to be mounted in a standard 19-inch equipment rack. The 3-slot chassis is 5.25 inches high, 19 inches wide and 17.5 inches deep.

Cooling is provided by a fan mounted on the left side of the chassis behind the Mini-panel.

The front panel snaps on and off. There are no screws or hinges holding it in place. No cabling exists between the front panel and the chassis since the Mini-panel is mounted directly onto the chassis and its controls are accessible through a slot on the left side of the front panel.

#### 1.3.1.5 Mini-Panel

The Mini-Panel on the POINT 4 MARK 3 chassis is used to control and monitor basic processor operation. It provides power controls and indicators, processor operation monitoring and program execution control. For further detail, see Section 3.2 on Mini-Panel operation.

The Virtual Control Panel allows monitoring and control of the processor from a master terminal, using the manipulator program MANIP. For further details see Section 3.3 on Virtual Control Panel operations.

# **Section 2** INSTALLATION

## 2.1 ENVIRONMENTAL REQUIREMENTS

Careful consideration must be given to the placement of the POINT 4 MARK 3 prior to installation to ensure that all power and environmental requirements are met. Necessary preinstallation considerations are discussed in the following subsections.

#### 2.1.1 POWER REQUIREMENTS

The POINT 4 MARK 3 requires a power source of 117 VAC, +10%, -15%; 47 to 63 Hz with 5 amperes current draw; or a 234 VAC, +10%, -15%; 47 to 63 Hz power source with 2.5 amperes current draw. In addition to power requirements for the POINT 4 MARK 3, the power resources and electrical outlets needed to handle all peripheral devices must be considered.

#### 2.1.2 TEMPERATURE REQUIREMENTS

Adequate environmental controls are needed to maintain the POINT 4 MARK 3 within the maximum operating range of 0 to 50 degrees C (32 to 122 degrees F), and relative humidity range of 10 to 90 percent, noncondensing.

#### 2.1.2 ENCLOSURE REQUIREMENTS

The POINT 4 MARK 3 is packaged in a 3-slot chassis, measuring 5.25 inches high, 19 inches wide, and 17.5 inches deep. The CPU/Memory PCB, Peripheral Interface Board, and Power Supply Board have the same dimensions: 14.5 inches x 12 inches.

## 2.2 UNPACKING INSTRUCTIONS

The POINT 4 MARK 3 receives a complete test and inspection prior to shipment. Inspect each unit for completeness and shipping damage prior to installation. Inspect each carton for any evidence of damage due to dropping, puncturing, or crushing. If damage is evident, contact the carrier and the POINT 4 Data Corporation Sales Representative for further instructions.

#### 2.2.1 UNPACKING THE CARTONS

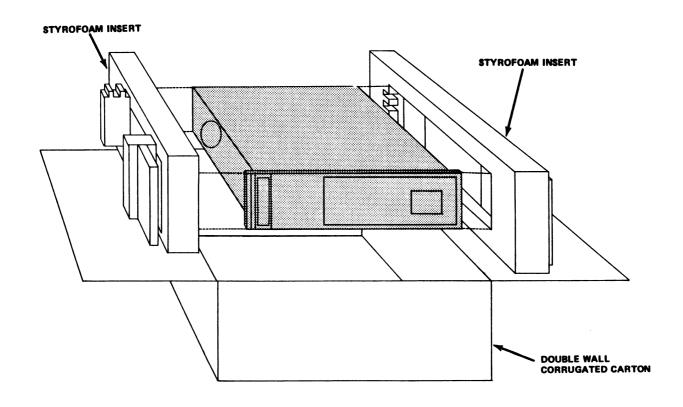

The POINT 4 MARK 3 is packaged in a double-walled corrugated carton. Styrofoam packing inserts surround the chassis. Figure 2-1 illustrates the processor chassis packaging.

#### 2.2.2 CONTAINER CONTENTS

Check each item removed from the carton against the packing slip. Inspect all items including cable connectors for damage. If items are damaged or broken, contact the POINT 4 Data Corporation Sales Representative.

Figure 2-1. POINT 4 MARK 3 Processor Chassis Packaging

## 2.3 MOUNTING INSTRUCTIONS

The processor is designed to be mounted in a standard 19-inch equipment rack. Although the exact procedure may vary, mount the chassis according to the following general procedure.

#### 2.3.1 FRONT PANEL

The POINT 4 MARK 3 front panel snaps off for easy removal. No screws or hinges hold it in place. Removing the front panel will reveal mounting slots on each side of the chassis (see Figure 2-2).

#### 2.3.2 CHASSIS

Once the front and back of the chassis have been sufficiently supported, flanges are available to secure the chassis to the cabinet.

Figure 2-2. POINT 4 MARK 3 Chassis Mounting Slots

## 2.4 MARK 3 INSTALLATION PROCEDURE

This section details the installation procedure for the MARK 3 system. It covers board checkout, connecting MUX cables, and powering up the system. See Section 2.6 for cabling diagrams and information. To upgrade an existing system, see Section 2.5.

If the MARK 3 to be installed has the extended capacity of 128KB memory and/or 7 ports, the CPU and/or the PIB board will have a piggyback expansion board. This does not change the installation procedure.

Before beginning with the installation procedure, make room on a table or other solid surface for the chassis and at least two boards.

#### 2.4.1 CHECKING THE BOARDS

The first phase in the installation process involves checking for damage and making sure everything is connected properly. An improper connection may cause damage when power is turned on.

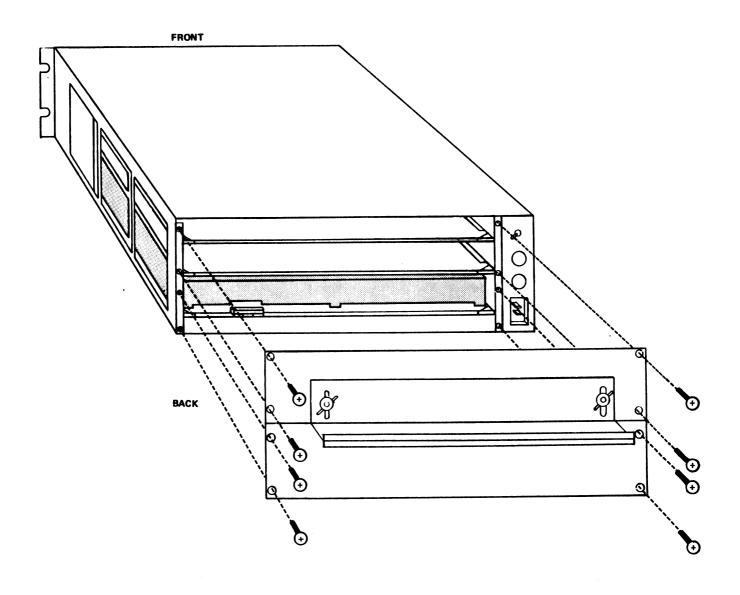

- 1. On the rear of the chassis, remove the eight screws holding the rear panels in place (see Figure 2-3).

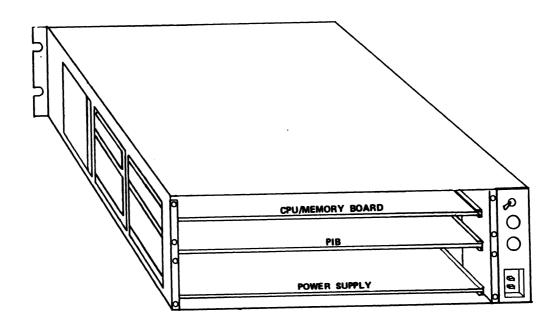

- 2. Remove both panels and set them aside. Three boards will be visible: in the first (top) slot is the CPU/Memory Board, in the second slot the Peripheral Interface Board (PIB), and in the third slot (bottom) the Power Supply Board (see Figure 2-4).

- 3. Pull out the white tabs at the sides of each board.

- 4. Check the CPU Board:

- a. Back-out the CPU board (top slot) and remove any packing material surrounding the board.

- b. Press down on each prom and any component using connectors to make sure it is seated properly. (Do not remove any, just press down on them.) Inspect the board for damage.

- c. If the CPU board has a Memory Expansion Board, make sure it is seated properly.

- d. Carefully reinstall the CPU board into slot 1, component side up, making sure that the card edge connectors slide smoothly into the backplane sockets.

Figure 2-3. POINT 4 MARK 3 Chassis with Rear Panel Open Showing Mounting Slots

Figure 2-4. POINT 4 MARK 3 Board Configuration

- 5. Check the Power Supply Board:

- a. Remove any packing material surrounding the Power Supply Board.

- b. Push in on the Power Supply Board to make sure it is connected properly.

- 6. Check the PIB Board:

- a. Back-out the PIB board and remove any packing material surrounding it.

- b. Press down on the header plugs to make sure they are seated properly.

- c. If the PIB board has a Port Expansion board, make sure it is seated properly.

- d. Slide the board back into slot 2, component side up, leaving approximately two or three inches extended.

#### 2.4.2 CONNECTING MUX CABLES

The next phase of the installation procedure is to connect the cables. For cabling information, see Section 2.6.

The MUX ports on the PIB are numbered 0-3. The expansion board ports are numbered 4-6. Port 0 is used as the master port; under IRIS, the printer is initially set up for Port 3.

#### NOTE

The printer may be connected to a port other than port 3 by changing the software (see the IRIS R7.5 Release Notes).

Please refer to Figure 2-5 for the position of connectors.

- 1. To connect the master port CRT, plug the cable into connector J5. This is the leftmost of the four white Molex connectors.

- 2. To connect the disc drive:

- a. Plug Cable "A" into connector J6 (60-pin, left side of PIB) with pin 1 of cable to the right edge of the connector. Make sure connector is not shifted to right or left.

- b. Plug Cable "B" into connector J8 (26-pin, behind J6) with pin 1 of cable to the right edge of the connector.

- c. If a second drive is to be connected, plug the second "B" cable into J7 (to the right of J8).

Figure 2-5. POINT 4 MARK 3 Peripheral Interface Board Connector Positions

- 3. To connect the streamer tape drive, plug the 50-pin cable into Jl (right side of PIB) with pin 1 to the right edge.

- 4. To connect the printer, plug its cable into J2 (white, 6-pin Molex).

- 5. The remaining ports are normally used for CRT terminals. a modem is used on the system, refer to section 2.6 for cabling considerations.

## NOTE

All MUX ports are strapped for 9600 baud. They may be restrapped if another rate is desired. See the MARK 3 Peripherals Interface Manual, Section 1.3.1.1, for baud rate selection change instructions.

- Push the PIB board back into the chassis. Make sure the card edge connectors slide smoothly into the backplane sockets.

- 7. Reinstall the two back panels.

#### 2.4.3 POWERING UP THE MARK 3 SYSTEM

It is necessary to make sure that all connectors are seated properly before the electrical current is turned on. An improper connection may result in damage. (See Section 2.4.1.)

The following steps should be followed when first applying power to the POINT 4 MARK 3 power supply and processor:

- Make sure the ON/OFF switch is turned to the OFF position.

- 2. Plug the AC cord into the rear right of the chassis.

- 3. Check that the grey cable connecting the mini-panel to the backplane is plugged in.

- 4. Turn the power switch at the rear of the chassis to the ON position. The POWER OK indicator should illuminate indicating that all voltages are in tolerance.

- 5. Turn the power-control switch on the Mini-panel to ON.

- The carry light comes on for approximately 1.5 seconds, goes off for .5 seconds, comes on again and remains illuminated.

- The Master CRT displays OK, indicating that the system has 7. run a successful CPU self-test program.

- 8. Run Self-Test (see Section 3.5).

- 9. Run diagnostics if the system has a tape drive (see the POINT 4 MARK 3 Diagnostics Manual).

- 10. If the disc drive has been turned on, has a system disc, and is in a Ready state, the MARK 3 will read block 0 from the disc and idle at location 377, waiting to be overwritten by DMA (standard IPL).

- 11. If the disc drive is not in a Ready state:

- a. Press the RESET button on the Mini-Panel, which accesses the MANIP program. The CRT displays the contents of the program counter and accumulators.

- b. Press P (program load from disc) on the CRT keyboard, followed by a <RETURN>. The MARK 3 will read block 0 from the disc and idle at location 377, waiting to be overwritten by DMA (standard IPL).

## 2.5 UPGRADING AN EXISTING MARK 3

A MARK 3 system may be upgraded to 128KB memory and/or seven MUX ports with expansion boards. If the existing CPU and PIB boards meet certain minimum specifications, expansion boards may be installed in the field.

Requirements and procedures given in this section are intended as quidelines. For specific information refer to the literature supplied with the expansion boards.

## 2.5.1 UPGRADING A MARK 3 TO 128KB MEMORY

If an existing 64KB MARK 3 system meets minimum requirements, it may be field-upgraded to 128KB memory by installing a Memory Expansion Board. These requirements and the installation procedure are outlined in the following sections.

## 2.5.1.1 Memory Expansion Requirements

Before the Memory Expansion Board is added, the following requirements must be met:

1. CPU board revision:

Any A or B Revision CPU board that has been brought up to ECO #465 can be field-graded. If the board has a jumper from 3H pin 6 to 2F pin 1 (part of ECO #465), the ECO is installed. If not, the board should be returned to POINT 4 for installation of all ECOs through #465. Call POINT 4 for a Return Authorization Number.

Any Revision C board can be field upgraded.

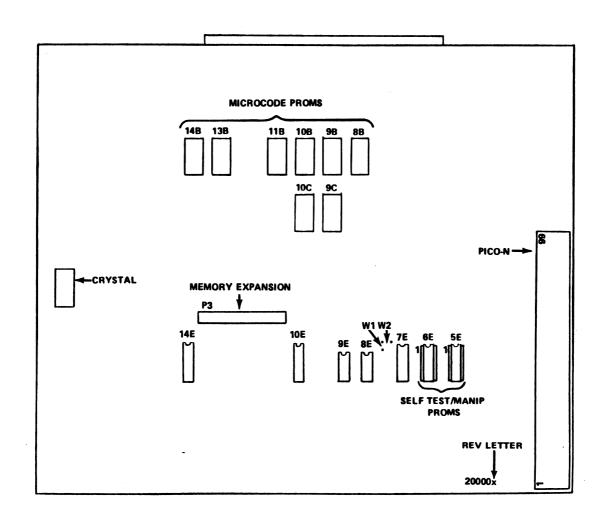

REV letter is located on extractor end of board "CPU 20000 \_".

- 2. Required CPU board parts (see Figure 2-6 for locations):

- Header plug at P3 (located between i.c. 10E and 14E). If there is no plug, one of the following may be installed:

| <u>Manufacturer</u> | <u>Part Number</u> |

|---------------------|--------------------|

| POINT 4             | 500350             |

| Berg                | 65610-150          |

- Correct Microcode and MANIP/Self-Test proms (refer to the instructions supplied with the Memory Expansion Board).

- Memory Expansion Board, POINT 4 P/N 20103.

- For IRIS users, the operating system must be R7.5 or later.

Figure 2-6. POINT 4 MARK 3 CPU Board

## 2.5.1.2 Memory Expansion Board Installation Procedure

To install the Memory Expansion Board, perform the following steps:

- 1. Test the system as follows:

- a. Run Self-Test on the CPU (see Section 3.5).

- b. Run Diagnostics on all devices on the PIB (see the POINT 4 MARK 3 Diagnostics Manual).

- 2. Remove the CPU board from the chassis.

- 3. Install header plug at P3, if necessary.

- 4. Move the Wl jumper (located between 7E and 8E) to W2 position.

#### NOTE

W1/W2 jumper must be set to one or the other, never to both.

- Wl position is for 64KB maximum

- W2 position is for 128KB maximum

- 5. Install the correct MANIP and Microcode proms (see instructions included with the Memory Expansion Board).

- 6. Plug Memory Expansion Board into 50-pin connector on CPU board and secure it with two screws (see Figure 2-7).

- 7. Make sure all plugable devices are fully inserted.

- 8. Reinstall CPU board in chassis.

- 9. Test the system as in step 1.

- 10. For IRIS users, modifications to the CONFIG file will be required to take advantage of additional memory space.

Figure 2-7. Installation of MARK 3 Memory Expansion and Port Expansion Boards

## 2.5.2 UPGRADING MARK 3 TO SEVEN PORTS

If an existing MARK 3 system meets minimum requirements, it may be field-upgraded to seven ports by installing the Port Expansion Board. These requirements and the installation procedure are discussed in the following sections.

## 2.5.2.1 MARK 3 Port Expansion Requirements

Before the Port Expansion Board is added, the following requirements must be met:

- CPU Board requirements (see Figure 2-6 for locations):

- Rev A and B CPU boards must have ECO #465 installed. the board has a jumper from 3H Pin 6 to 2F Pin 1 (part of ECO #465), the ECO is installed. If not, the board should be returned to POINT 4 for installation of all ECOs through #465. Call POINT 4 for a Return Authorization Number.

Rev C or later CPU board does not require any ECOs to use expansion boards.

## NOTE

Rev letter is located on extractor end of board "CPU 20000  $\_$ ".

- b. Correct Microcode proms (refer to the instructions supplied with the Port Expansion Board for details).

- PIB Board requirements (see Figure 2-5 for locations):

- Revision A PIB boards require a factory modification before the Port Expansion Board can be installed. Call POINT 4 for a Return Authorization Number.

Any Revision B (or later) PIB board can be field-upgraded.

## NOTE

Rev B or later boards have rev letter marked on board, behind Jl, following part number "PIB 21000 \_".

b. Connector at J9 - if missing, one must be installed.

| <u>Manufacturer</u> | Part Number |

|---------------------|-------------|

| POINT 4             | 500350      |

| Berg                | 65610-150   |

- c. DIP headers or push-on plugs to set baud rate on expansion ports.

- d. Port Expansion Board, POINT 4 P/N 21100.

- 3. Software requirements:

- a. For IRIS users, this option requires version R7.5 (or later) and proper MUX driver.

## 2.5.2.2 Port Expansion Board Installation Procedure

To install the Port Expansion Board, perform the following steps:

- 1. Test the system as follows:

- a. Run Self-Test on the CPU (see Section 3.5).

- b. Run Diagnostics on all I/O devices on the PIB (see the POINT 4 MARK 3 Diagnostics Manual).

- 2. Remove CPU board from chassis:

- a. Install correct Microcode proms in CPU board.

- b. Make sure that all plugable devices are fully inserted.

- c. Reinstall CPU board in chassis and test CPU board.

- 3. Remove PIB board from chassis:

- a. Install header plug at J9, if necessary.

- b. Plug Port Expansion Board into 50-pin connector on PIB and secure with two screws (see Figure 2-7).

- c. Install baud rate jumpers at locations J10, J11, J12.

- d. Make sure that all plugable devices are fully inserted.

- e. Reinstall PIB board in chassis and attach cables (see Section 2.6).

- 4. Retest system as in step 1.

## 2.6 PIB CABLING

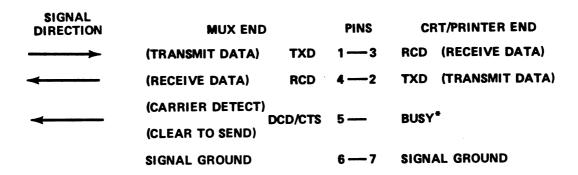

The MUX ports on Revisions A through C of the PIB board have two status inputs and no output. MUX ports on Revision D PIBs and all Port Expansion Boards have one status input and one control output. The new output bit is particularly useful for modem control (DTR).

Cables for Rev A-C PIBs have pins 2 and 5 jumpered together. The jumper should be removed for new-style ports (Rev D (or later) and for all Port Expansion Board ports).

Table 2-1 is a guide for cable, port type, and device usage. Cables are for standard configuration; nonstandard devices may have different cabling requirements.

Figures 2-8 through 2-10 illustrate standard cable wiring for the MARK 3.

The PIB or Expansion Board end of the MUX cable uses a 6-pin connector:

|                                             | Molex P/N  | POINT 4 P/N |

|---------------------------------------------|------------|-------------|

| Connector, 6-pin                            | 09-50-3061 | 500106      |

| Pin, crimp type (one pin per wire required) | 08-50-0106 | 724005      |

The other end of the cable uses a standard RS-232 DB-25 connector.

See Appendix A for cable length considerations.

TABLE 2-1. MARK 3 CABLE USAGE

|         | PIB<br>Rev A-C<br>Ports 0-3 | PIB, Rev D<br>(or later)<br>Ports 0-3 | All Port<br>Expansion<br>Ports 4-6 |

|---------|-----------------------------|---------------------------------------|------------------------------------|

| CRT     | 1 or 2                      | 1 or 2                                | 1 or 2                             |

| Printer | l or 2                      | 2                                     | 2                                  |

| Modem   | *                           | 3                                     | 3                                  |

## where

- 1 MARK 3 asynchronous CRT/printer cable for Ports 0-3

on Revision A thru C PIBs (see Figure 2-8).

- 2 MARK 3 asynchronous CRT/printer cable for Ports 0-3 on Revision D (or later) PIBs; and Ports 4-6 on all Port Expansion Boards (see Figure 2-9).

- 3 MARK 3 asynchronous modem cable for Ports 0-3 on Revision D (or later) PIBs; and Ports 4-6 on all Port Expansion Boards (see Figure 2-10).

- \*A modem may function on Rev A-C PIBs if the modem does not require a control line from the computer (no DTR required); in that case, use cable 3.

| SIGNAL DIRECTION | MUX END          |     | PINS | CR   | T/PRINTER END   |

|------------------|------------------|-----|------|------|-----------------|

|                  | (TRANSMIT DATA)  | TXD | 13   | RCD  | (RECEIVE DATA)  |

| <del></del>      | (RECEIVE DATA)   | RCD | 42   | TXD  | (TRANSMIT DATA) |

| <del></del>      | (CARRIER DETECT) | DCD | 2    | BUSY | •               |

| <del></del>      | (CLEAR TO SEND)  | CTS | 5    |      |                 |

|                  | SIGNAL GROUND    |     | 67   | SIGN | AL GROUND       |

## \*BUSY:

CRTs - NOT REQUIRED PRINTERS - NORMALLY PIN 19 OR 20 MAY ALSO BE 11 OR 14 (CONSULT YOUR PRINTER MANUAL) PRINTER BUSY MUST BE:

NORMAL = HIGH BUSY = LOW

## NOTE

THIS CABLE SHOULD ALSO WORK WITH CRTs ON REV D OR LATER PIB BOARDS FOR ALL SEVEN PORTS; IT WILL NOT WORK WITH PRINTERS ON REV D OR LATER BOARDS.

Figure 2-8. MARK 3 Asynchronous CRT/Printer Cable Ports 0-3, PIB Revisions A thru C

\*BUSY:

CRTs - NOT REQUIRED

PRINTERS - NORMALLY PIN 19 OR 20

MAY ALSO BE 11 OR 14

(CONSULT YOUR PRINTER MANUAL)

PRINTER BUSY MUST BE:

NORMAL = HIGH

BUSY = LOW

Figure 2-9. MARK 3 Asynchronous CRT/Printer Cable Ports 0-3, PIB Revision D (and later) Ports 4-6, All Port Expansion Boards

| SIGNAL DIRECTION | MUX END                                      |        | PINS  |      | MODEM END             |

|------------------|----------------------------------------------|--------|-------|------|-----------------------|

| <del></del>      | (TRANSMIT DATA)                              | TXD    | 1 2   | TXD  | (TRANSMIT DATA)       |

|                  | (RECEIVE DATA)                               | RCD    | 43    | RCD  | (RECEIVE DATA)        |

|                  | (REQUEST TO SEND)<br>RT<br>(DATA TERMINAL RE |        | 2-20  | DTR  | (DATA TERMINAL READY) |

| 4                | (CARRIER DETECT) DO (CLEAR TO SEND)          | CD/CTS | 5 —8  | DCD  | (CARRIER DETECT)      |

|                  | SIGNAL GROUND                                |        | 6 — 7 | SIGN | AL GROUND             |

#### NOTE

IF A MODEM IS REQUIRED ON A REV A—C PIB, AND EXPANSION PORTS ARE NOT AVAILABLE, THE MODEM USED MUST NOT REQUIRE ANY CONTROL LINE FROM THE COMPUTER. IT MUST BE JUMPERED OR SWITCHED TO BE READY CONSTANTLY (NO DTR REQUIRED).

Figure 2-10. MARK 3 Asynchronous Modem Cable Ports 0-3, PIB Revision D (and later) Ports 4-6, All Port Expansion Boards

# Section 3 OPERATING PROCEDURES

## 3.1 INTRODUCTION

The POINT 4 MARK 3 Computer has two means of control:

- Mini-Panel on MARK 3 chassis

- Virtual Control Panel via Master Terminal

This section describes the Mini-Panel controls and indicators, and provides procedures for performing common types of operations through the Virtual Control Panel. In addition, instructions and procedures for Processor/CTU interface are included.

This section also contains instructions for diagnostic checks.

## 3.2 MINI-PANEL

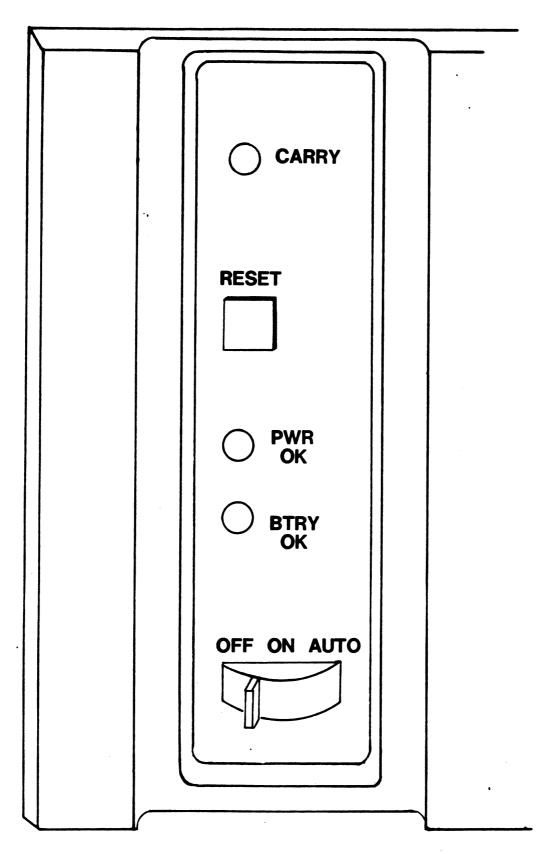

The POINT 4 MARK 3 chassis houses essential controls and indicators for basic processor operation. The controls and indicators of the Mini-panel are located on the left-hand side of the chassis (see Figure 1-1). There are three types of operating functions on the Mini-panel: power controls and indicators, processor operation monitoring, and program execution controls. Figure 3-1 is an illustration of the Mini-panel controls and indicators.

Figure 3-1. POINT 4 MARK 3 Mini-Panel

## 3.2.1 POWER CONTROLS AND INDICATORS (POWER SWITCH/PWR OK LIGHT)

The Mini-panel contains power controls and indicators. Power ON is controlled by a three-position switch. Table 3-1 lists the three functions of the power control switch.

A Light Emitting Diode (LED) indicator illuminates to indicate that all DC voltages are in tolerance. Table 3-2 shows the interpretations of the PWR OK LED.

See Figure 3-1 for an illustration of the three-position switch and the PWR OK indicator.

TABLE 3-1. POWER CONTROL SWITCH FUNCTIONS

| Switch<br>Setting | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON                | Turns on power to the processor and places the Mini-panel in the Panel-On Mode. In this mode all controls and indicators on the Mini-panel are enabled. One pass of Self-test is executed, the carry light illuminates once and goes off, and the message OK is displayed on the port O terminal. If a disc drive is connected and operational, an automatic IPL (initial program load) is performed when the power control switch is set to ON. |

| AUTO              | Same as ON.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OFF               | Turns off the power supply and thus all processor and Mini-panel functions.                                                                                                                                                                                                                                                                                                                                                                      |

TABLE 3-2. POWER OK LED INTERPRETATIONS

| PWR OK | Interpretation                                                                                                                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF    | Power supply not connected to AC.                                                                                                                                    |

| OFF    | This condition (if power control switch is set to ON or AUTO position and AC plug is connected) indicates that one of the power supply voltages is out of tolerance. |

| ON     | All power supply voltages are in tolerance and available to the processor chassis.                                                                                   |

## 3.2.2 PROCESSOR OPERATION MONITORING (CARRY LIGHT)

In addition to the power monitoring indicators discussed above, the Mini-panel has an LED indicator for monitoring the carry state of processor operation. This LED is enabled in the Panel-On Mode (power control switch set to ON or AUTO) and disabled in the Panel-Off Mode (power control switch set to OFF). It indicates the current state of the processor carry flag. The LED illuminates when the carry flag is set to 1 (one). See Figure 3-1 for location of the carry indicator.

## 3.2.3 PROGRAM EXECUTION CONTROL (RESET SWITCH)

A pushbutton switch is available to reset program execution in the processor. This switch is enabled in the Panel-On Mode (power control switch set to ON or AUTO position) and disabled in the Panel-Off Mode (power control switch set to OFF position).

Pressing RESET loads the contents of an octal debugger/manipulator/self-test PROM into the top 1000 (octal) words of memory. The debugger/manipulator is used for access to accumulators and memory, allowing examination and deposit of data for operation monitoring and control. It optionally allows loading of system software from disc. See Section 3.3 for debugger/manipulator program commands and Section 3.5 for self-test diagnostic capabilities.

See Figure 3-1 for location of the RESET switch.

## 3.2.4 BATTERY MONITORING INDICATOR (BTRY OK LIGHT)

A battery monitoring indicator is present on the Mini-panel. This indicator is nonfunctional since battery backup is not available on the POINT 4 MARK 3.

## 3.3 VIRTUAL CONTROL PANEL

The POINT 4 MARK 3 has the ability to perform many front panel operations plus some system monitoring functions from a master terminal. This feature is designed for use by computer operators and programmers to debug system problems and to manipulate the contents of registers and memory. The feature is implemented in a stand-alone program called MANIP which is loaded into RAM from a PROM when the RESET switch is pressed or when a "HALT" instruction is executed.

## 3.3.1 MANIP PROGRAM

MANIP is a simple but powerful position-independent memory manipulator and debug package. MANIP occupies only 1000 (octal) words of memory.\* All operations are executed by typing one letter followed by octal parameters as required (except colon (:) which is also preceded by an octal parameter) and ending with a <RETURN>.

Table 3-3 lists the functions provided by MANIP (the number in the right column indicates the number of parameters required for that particular function).

MANIP normally occupies the memory locations 77000 through 77777. Location 77000 is reserved for saving the initial value of the program counter (PC), that is, the value of PC where the CPU was executing before MANIP was started. MANIP may be moved at any time by use of its MOVE (M) instruction.

The carry light flashes while MANIP is waiting for an input character to be entered. This is a signal that MANIP is active and will respond to input.

If an error is made while entering control information, two choices are available for correcting it:

- Press <ESC> (or any other control character except <RETURN>) to delete the type-in and enable a new type-in.

- 2. If the error was made in entering an octal value, type a few zeros followed by the correct octal number. MANIP will only use the last six octal digits entered for the octal word.

<sup>\*</sup>For those who are familiar with POINT 4's IRIS Operating System, MANIP is comparable to DBUG. The main differences are that MANIP does not have (1) symbolic capability, (2) breakpoints or trace, (3) disc read or write, (4) virtual addressing, and (5) <CTRL-H>/<CTRL-A> (backspace) capability. MANIP occupies only 1000 (octal) words of memory, while DBUG occupies 3000 (octal) words of memory.

TABLE 3-3. SUMMARY OF MANIP COMMAND FUNCTIONS

| Code | Function                                             | Parameters<br>Required |

|------|------------------------------------------------------|------------------------|

| A    | Display initial PC, accumulators and carry flip-flop | (0)                    |

| С    | Change accumulator or carry flip-flop                | (2)                    |

| D    | Dump (octal, word or byte)                           | (1)                    |

| Н    | Reads block 0 from Archive                           | (0)                    |

| J    | Jump with accumulators and carry restored            | (1)                    |

| K    | Store a constant in a block of memory                | (3)                    |

| М    | Move a block in memory                               | (3)                    |

| P    | Program load from disc                               | (0)                    |

| R    | Read 3 blocks from CTU                               | (0)                    |

| т    | Run Self-test program                                | (0)                    |

| :    | Examine or deposit into a specified location         | (1:1)                  |

## 3.3.2 MANIP COMMAND DESCRIPTIONS

A MANIP command consists of a single letter which is the command identifier and parameters which specify memory addresses and data input. All parameters must be entered in octal form. The letters x, y, and z are used to represent octal parameters. Press <RETURN> after entering any command. Table 3-4 lists each MANIP command and its definition.

TABLE 3-4. MANIP COMMANDS

| Command &<br>Parameters | Definition                                                                                                                                                                                                                             |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A                       | Causes the initial value of PC (program counter) saved in first location of MANIP, the contents of accumulators AO, Al, A2, A3, and the carry flip-flop as they were at the time MANIP was entered to be typed on the master terminal. |

| Cx,y                    | Change accumulator or carry flip-flop:                                                                                                                                                                                                 |

|                         | <ul> <li>If x is 0, 1, 2, or 3, then y is stored as<br/>saved value for accumulator x (A0, A1, A2,<br/>A3, respectively).</li> </ul>                                                                                                   |

|                         | <ul> <li>If x is 4, then saved value of the carry<br/>flip-flop is set equal to the LSB of y</li> </ul>                                                                                                                                |

|                         | <ul> <li>Parameter Description</li> <li>x - l octal digit 0-4</li> <li>y - l word octal</li> </ul>                                                                                                                                     |

| Dχ                      | Dump memory in octal, beginning at location x. Eight words are typed per line, with the address of the first word at the beginning of each line.                                                                                       |

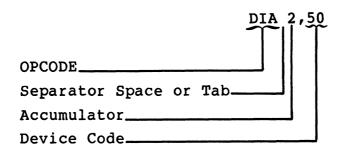

|                         | <ul> <li>Parameter Description</li> <li>x - octal number representing a 16-bit memory address</li> </ul>                                                                                                                               |