# MIGHTY MUX DMA MULTIPLEXER USER MANUAL

BRENDA

# POINT 4 DATA CORPORATION

2569 McCabe Way / Irvine, California 92714

# MIGHTY MUX DMA MULTIPLEXER USER MANUAL

#### NOTICE

Every attempt has been made to make this reference manual complete, accurate and up-to-date. However, all information herein is subject to change due to updates. All inquiries concerning this manual should be directed to POINT 4 Data Corporation.

Copyright © 1977, 1982 by POINT 4 Data Corporation (formerly Educational Data Systems, Inc). Printed in the United States of America. All rights reserved. No part of this work covered by the copyrights hereon may be reproduced or copied in any form or by any means--graphic, electronic, or mechanical, including photocopying, recording, taping, or information and retrieval systems--without the written permission of:

> POINT 4 Data Corporation 2569 McCabe Way Irvine, CA 92714 (714) 754-4114

### **REVISION RECORD**

PUBLICATION NUMBER: HM-042-0015

Description Date Revision

Update of original manual (1977) 08/30/82

#### LIST OF EFFECTIVE PAGES

Changes, additions, and deletions to information in this manual are indicated by vertical bars in the margins or by a dot near the page number if the entire page is affected. A vertical bar by the page number indicates pagination rather than content has changed.

| <u>Page</u>    | Rev | <u>Page</u> | Rev | <u>Page</u> | <u>Rev</u> |

|----------------|-----|-------------|-----|-------------|------------|

|                |     |             |     |             |            |

| Cover          | _   |             |     |             |            |

| Title          | _   |             |     |             |            |

| ii thru xi     | A   |             |     |             |            |

| 1-1 thru 1-10  | Α   |             |     |             |            |

| 2-1 thru 2-28  | Α   |             |     |             |            |

| 3-1 thru 3-46  | A   |             |     |             |            |

| Appendix Title | _   |             |     |             |            |

| A-1 thru A-3   | Α   |             |     |             |            |

| B-1            | A   |             |     |             |            |

| C-1            | A   |             |     |             |            |

| D-1            | Α   |             |     |             |            |

| Comment Sheet  | A   |             |     |             |            |

| Mailer         | _   |             |     |             |            |

| Back Cover     | _   |             |     |             |            |

#### PREFACE

This manual includes general reference information for the POINT 4 MIGHTY MUX DMA Multiplexer. It describes system architecture, input/output interface, and specifications. It discusses aspects of hardware interface including installation, I/O bus interface signals, junction panel connections, hardware-selectable options and multiplexer timing. Programming information is also included.

Related manuals include:

| <u>Title</u>                                         | Pub. Number           |

|------------------------------------------------------|-----------------------|

| MIGHTY MUX Diagnostics Manual<br>POINT 4 User Manual | HM-042-0007<br>(1979) |

| POINT 4 MARK 8 Reference Manual                      | HM-082-0021           |

### **CONTENTS**

| <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                            | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GENERAL DESCRIPTION Features Multiplexer Models Multiplexer Operation SYSTEM ARCHITECTURE INPUT/OUTPUT INTERFACE SPECIFICATIONS                                                                                                                                                                                                                                                                                         | 1-1<br>1-4<br>1-5<br>1-6<br>1-7<br>1-9<br>1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INTRODUCTION MEMORY ALLOCATION REQUIREMENTS INPUT/OUTPUT PROCESSING SEQUENCE CONTROL WORD DEFINITIONS Input Control Word (ICW) Output Control Word (OCW) Input Byte Pointer (IBP) - Word 4 of Control Block Output Byte Pointer (OBP) - Word 5 of Control Block Last Input Byte (LIB) - Word 6 of Control Block Last Output Byte (LOB) - Word 7 of Control Block Status Word Definitions                                | 2-1<br>2-1<br>2-3<br>2-5<br>2-5<br>2-11<br>2-16<br>2-16<br>2-16<br>2-16<br>2-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INSTRUCTIONS FOR CPU CONTROL OF MUX INITIALIZATION PROCEDURES Input and Output Initialization Input in Single-Character Mode Output in Single-Character Mode Input Automatically Into a String Buffer Output Automatically From a String Buffer Change Port Control Parameters Interrupt Service MASTER TERMINAL MODE INSTRUCTIONS/PROCEDURES Input Output Master Terminal Mode-to-Mux Mode Mux-to-Master Terminal Mode | 2-19<br>2-22<br>2-23<br>2-23<br>2-24<br>2-25<br>2-25<br>2-26<br>2-27<br>2-27<br>2-27<br>2-28<br>2-28<br>2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | INTRODUCTION  GENERAL DESCRIPTION Features Multiplexer Models Multiplexer Operation SYSTEM ARCHITECTURE INPUT/OUTPUT INTERFACE SPECIFICATIONS  PROGRAMMING  INTRODUCTION MEMORY ALLOCATION REQUIREMENTS INPUT/OUTPUT PROCESSING SEQUENCE CONTROL WORD DEFINITIONS  Input Control Word (ICW) Output Control Word (OCW) Input Byte Pointer (IBP) - Word 4 of Control Block Output Byte Pointer (OBP) - Word 5 of Control Block Last Input Byte (LIB) - Word 6 of Control Block Last Output Byte (LOB) - Word 7 of Control Block Status Word Definitions INSTRUCTIONS FOR CPU CONTROL OF MUX INITIALIZATION PROCEDURES Input and Output Initialization Input in Single-Character Mode Output in Single-Character Mode Output in Single-Character Mode Input Automatically Into a String Buffer Output Automatically From a String Buffer Change Port Control Parameters Interrupt Service MASTER TERMINAL MODE INSTRUCTIONS/PROCEDURES Input Output Master Terminal Mode-to-Mux Mode |

| 3                  | HARDWARE INTERFACE                               | 3-1        |

|--------------------|--------------------------------------------------|------------|

| 3.1                | INTRODUCTION                                     | 3-1        |

|                    | MIGHTY MUX ARCHITECTURE                          | 3-2        |

| 3.3                |                                                  | 3-4        |

| 3.3.1              |                                                  | 3-4        |

|                    |                                                  | 3-4        |

| 3.3.1.1            |                                                  | 3-4        |

| 3.3.1.2            |                                                  | 3-4<br>3-4 |

| 3.3.1.3            |                                                  |            |

| 3.3.1.4            |                                                  | 3-6        |

| 3.3.1.5            |                                                  | 3-6        |

| 3.3.1.6            |                                                  | 3-6        |

| 3.3.1.7            |                                                  | 3-7        |

| 3.3.2              | Additional Considerations                        | 3-8        |

| 3.3.2.1            |                                                  | 3-8        |

| 3.3.2.2            |                                                  | 3-8        |

| 3.3.2.3            |                                                  | 3-8        |

| 3.3.2.4            |                                                  | 3-8        |

| 3.4                | MULTIPLEXER SYSTEM CONFIGURATION                 | 3-10       |

| 3.5                | INPUT/OUTPUT BUS INTERFACE SIGNALS               | 3-11       |

| 3.5.1              | Input/Output Interface Signal Classification     | 3-11       |

| 3.5.2              | Backplane Pin Signal Connection                  | 3-17       |

| 3.6                | JUNCTION PANEL CONNECTIONS                       | 3-19       |

| 3.6.1              | MIGHTY MUX-to-Terminal Connections               | 3-19       |

| 3.6.2              | MIGHTY MUX-to-Modem Connections                  | 3-19       |

| 3.6.3              | Current Loop Connections                         | 3-21       |

| 3.7                | HARDWARE-SELECTABLE OPTIONS                      | 3-22       |

| 3.7.1              | Master Terminal Mode Removal Option              | 3-23       |

| 3.7.2              | 19.2K Baud-Rate Option (B Option)                | 3-24       |

| 3.7.3              | Device Code Options                              | 3-25       |

| 3.7.4              | Master Terminal Mode Device Code 50/51 Option    |            |

| 3.7.5              | Mask Bit Option                                  | 3-27       |

| 3.7.6              | Port Control Block Length Option                 | 3-28       |

| 3.7.6.1            | 20-Word (Octal) Block Length                     | 3-28       |

| 3.7.6.1<br>3.7.6.2 | 10-Word (Octal) Block Length                     | 3-28       |

| 3.7.7              | Control Block Area Location Option               | 3-29       |

| 3.7.8              | Port Control Block Location Option               | 3-31       |

| 3.7.9              | Special Character Set Options                    | 3-33       |

| 3.7.9.1            | Special Character Set Usage                      | 3-33       |

| 3.7.9.2            | Special Character Set Implementation             | 3-34       |

| 3.7.10             | MSB in ASCII Mode Option                         | 3-35       |

| 3.7.11             | X Option                                         | 3-36       |

| 3.7.12             | 128KB-Addressing MUX Buffer Allocation Option    | 3-30       |

| 3.7.12             | Isochronous Option                               | 3-37       |

| 3.7.14             | On-Board Power Option                            | 3-30       |

| 3.8                | MULTIPLEXER TIMING AND ELECTRICAL SPECIFICATIONS | 3-40       |

| 3.8.1              |                                                  |            |

|                    | Input/Output Timing Specifications               | 3-41       |

| 3.8.2              | Electrical Specifications                        | 3-41       |

| 3.8.3              | Overall MUX Timing                               | 3-43       |

| 3.8.4              | Maximum Data Rate Per Port                       | 3-45       |

#### **APPENDICES**

| A                        | MUX DIAGNOSTICS                                                                                                                                | A-1                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A.1<br>A.2<br>A.3<br>A.4 | MUX Diagnostic Cable Connections<br>Mini-Test Using Computer Front Panel<br>Mini-Test Using Virtual Front Panel<br>Control Area Search Program | A-1<br>A-2<br>A-2<br>A-3 |

| В                        | CABLE LENGTH CONSIDERATIONS                                                                                                                    | B-1                      |

| С                        | ASCII CODE CHART                                                                                                                               | C-1                      |

| D                        | ACRONYMS AND ABBREVIATIONS                                                                                                                     | D-1                      |

#### **FIGURES**

| Number | <u>Title</u>                                                                                           | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

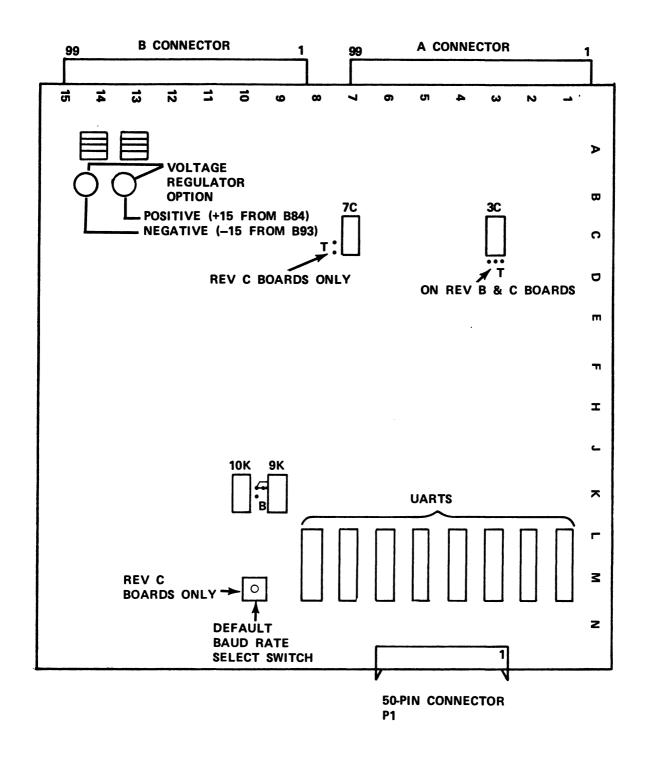

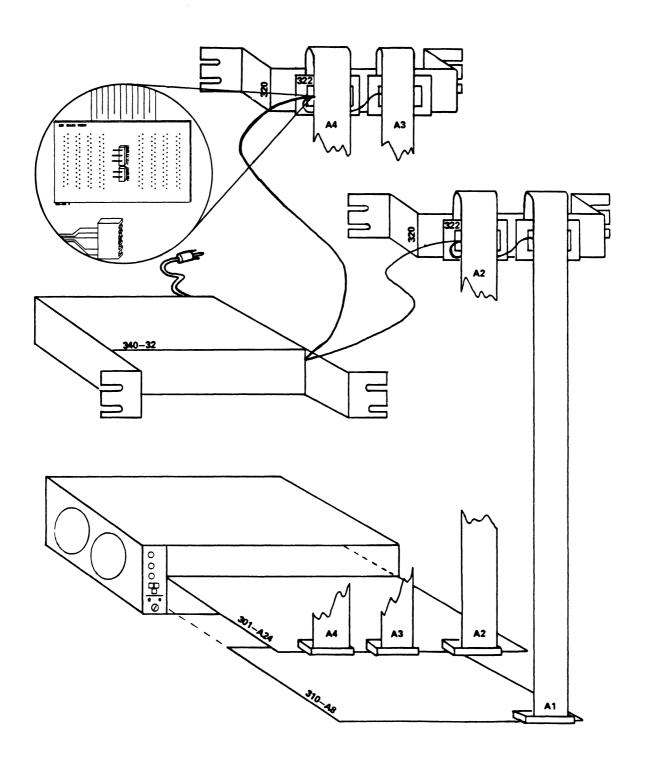

| 1-1    | MIGHTY MUX 310-A8 Board                                                                                | 1-2  |

| 1-2    | MIGHTY MUX 24-Port System, With 310-A8 and 301-A16 Boards                                              | 1-3  |

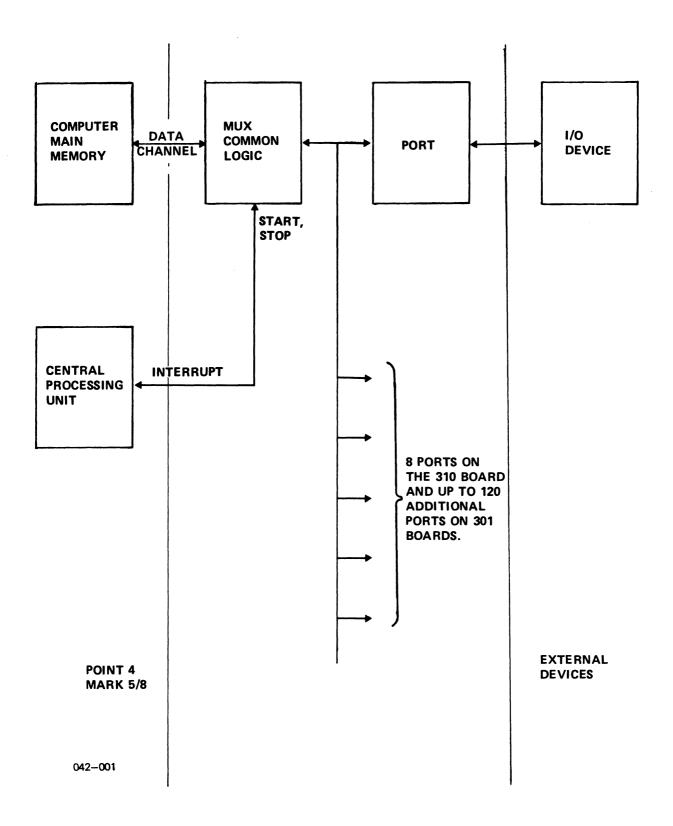

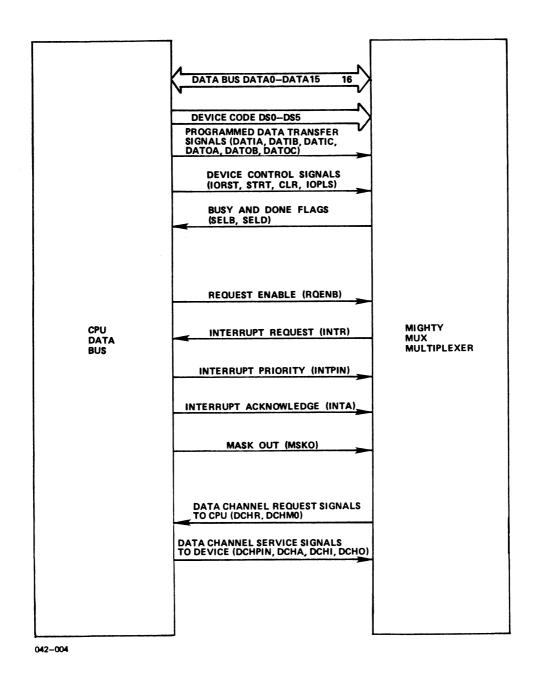

| 1-3    | System Block Diagram of the MIGHTY MUX Interfacing External Devices to POINT 4 and Nova-type Computers | 1-8  |

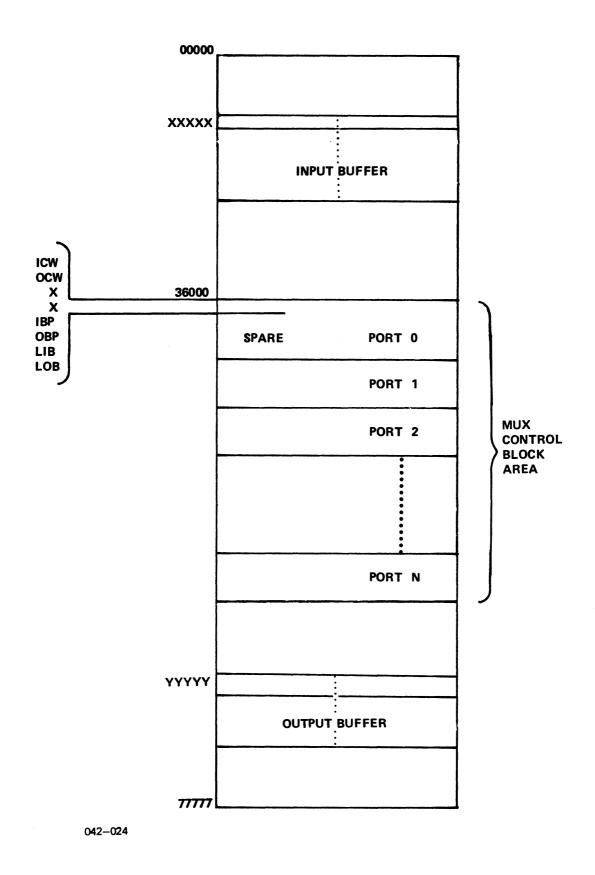

| 2-1    | Memory Allocation for Control Block and<br>Input and Output Buffers                                    | 2-2  |

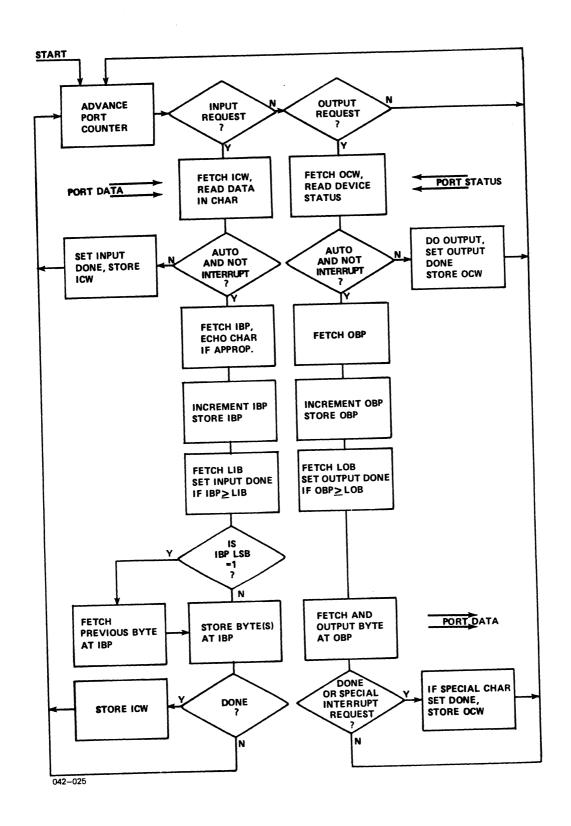

| 2-2    | Input/Output Processing Flowchart                                                                      | 2-4  |

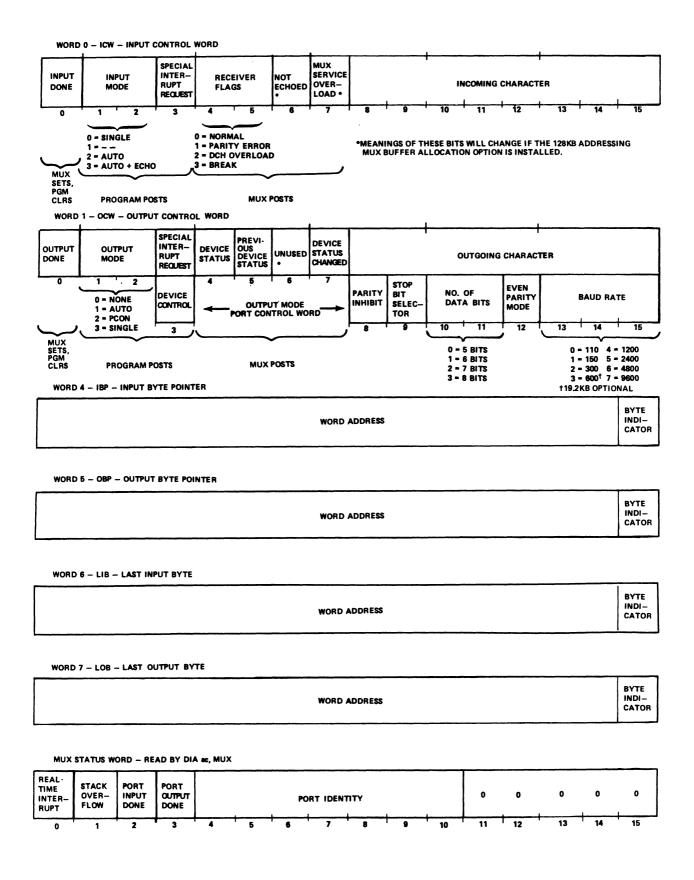

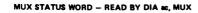

| 2-3    | MIGHTY MUX Control Words                                                                               | 2-6  |

| 2-4    | MUX Status Word                                                                                        | 2-17 |

| 2-5    | OCW Example                                                                                            | 2-22 |

| 3-1    | MIGHTY MUX Logic Block Diagram                                                                         | 3-3  |

| 3-2    | Multiplexer Installation                                                                               | 3-5  |

| 3-3    | Backplane Connections for 301 Board                                                                    | 3-7  |

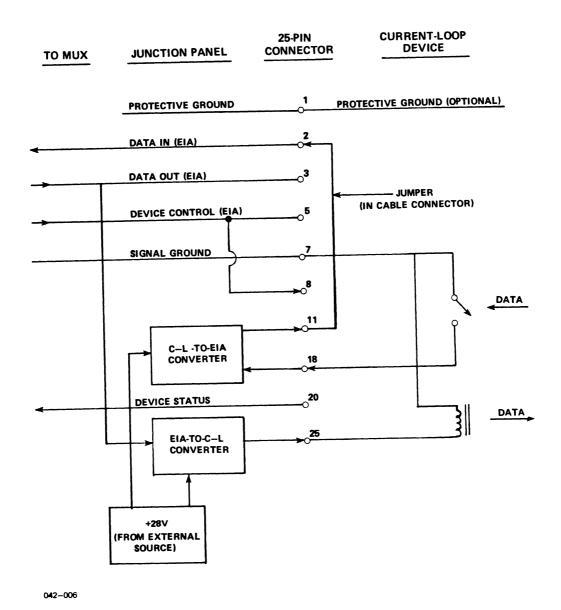

| 3-4    | Junction Panel Connections for<br>Current-Loop Interfaces                                              | 3-9  |

| 3-5    | MUX Configuration Guide                                                                                | 3-10 |

| 3-6    | Input/Output Signals                                                                                   | 3-12 |

| 3-7    | Backplane I/O Signals                                                                                  | 3-18 |

| 3-8    | MUX-to-Terminal Connections                                                                            | 3-20 |

| 3-9    | MUX-to-Modem Connections                                                                               | 3-20 |

| 3-10   | Disabling of Master Terminal Mode                                                                      | 3-23 |

| 3-11   | Optional ICW and OCW Formats                                                                           | 3 23 |

|        | For MUX Buffer Allocation Option                                                                       | 3-37 |

| 3-12   | Isochronous Option Implementation                                                                      | 3-39 |

| 3-13   | Block Diagram of EIA Interface                                                                         | 3-42 |

| 3-14   | Current-Loop Circuitry                                                                                 | 3-42 |

| 3-15   | Overall Timing Diagram                                                                                 | 3-44 |

| 3-16   | Relationship Between Number of Ports and                                                               |      |

| _ 5    | Maximum Data Rate Per Port                                                                             | 3-46 |

#### **TABLES**

| Number | Title                                  | Page |

|--------|----------------------------------------|------|

| 2-1    | Input Control Word Definitions         |      |

|        | (Word 0 of Each Control Block)         | 2-7  |

| 2-2    | Output Control Word Definitions        |      |

|        | (Word 1 of Each Control Block)         | 2-11 |

| 2-3    | MUX Status Word Definitions            | 2-18 |

| 2-4    | CPU Control of MUX                     | 2-19 |

| 3-1    | Input/Output Signals by Classification | 3-13 |

## Section 1 INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

POINT 4 Data's MIGHTY MUX Multiplexer is a general purpose communications front-end for POINT 4 and Nova\*-type computers. From four to 128 peripheral devices can be interfaced to the processor via the Direct Memory Access (DMA) channel, thus reducing I/O processing overhead on the CPU. A MIGHTY MUX system can handle up to 128 ports at 9600 baud, or up to 64 ports at 19.2K baud, all operating simultaneously.

The MIGHTY MUX consists of a Model 310 basic multiplexer with optional expansion boards (Model 301 series) for additional asynchronous ports. Model 310 is available as either a four-port (310-A4) or an eight-port (310-A8) controller. The 310 has, as standard features, a real-time clock, master terminal interface, and four or eight asynchronous serial ports which can handle CRTs, printing terminals, serial printers with RS-232 interface, or modem controls.

The following port parameters are under program control on a port-by-port basis: I/O buffer size and location, character size, parity, auto echo, interrupt conditions, and baud rate (a user can sign onto the system at one baud rate and switch to any other standard baud rate from the terminal).

The MIGHTY MUX multiplexer is software-compatible with the IRIS (Interactive Real-Time Information System) Operating System used on POINT 4 MARK 5/8 and Nova-type computers.

Throughput is limited primarily by the system software capabilities, since data-transfer handling is block oriented, rather than character-by-character oriented. The requirements for software handling of the transfer are reduced to starting transmission by setting appropriate control words, and receiving an interrupt when transmission is completed.

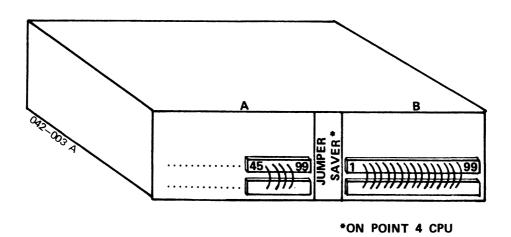

Figure 1-1 is an illustration of the MIGHTY MUX 310-A8 board. Figure 1-2 is a photograph of a 24-port system, consisting of 310-A8 and 301-A16 boards.

<sup>\*</sup>Nova is a registered trademark of Data General Corporation.

Figure 1-1. MIGHTY MUX 310-A8 Board

Figure 1-2. MIGHTY MUX 24-Port System, With 310-A8 and 301-A16 Boards

#### 1.1.1 FEATURES

The MIGHTY MUX DMA Multiplexer greatly expands system performance capabilities. Its advanced design and versatility are evident in the following features:

- Direct memory access capability

- Interfaces terminals, line printers, modems

- Supports mixed line speeds and code levels

- Line speeds up to 9600 baud (19.2K baud optional)

- Supports character or block-oriented I/O tasks

- Single MIGHTY MUX 310 board includes four or eight multiplexer ports

- Expandable up to 128 ports

- Master Terminal Mode permits use of Port 0 as the master terminal interface (device code 10/11) or as a multiplexer port

- Software control of six port parameters

- Expansion boards offer 8, 16, or 24 ports per board

- Modem control available on each port

- Control character recognition

- Compatible with EIA RS-232C/CCITT V.24 or current loop (20, 40 or 60 milliamps)

- Switch-selectable master terminal baud rate

#### 1.1.2 MULTIPLEXER MODELS

The MIGHTY MUX Multiplexer is available in several configurations. All configurations use the Model 310 basic multiplexer. Available models and their features are listed below. (See the Configuration Guide in Section 3.4.)

| Model   | Description                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 310-A4  | 4-port multiplexer (nonexpandable)                                                                                                                         |

| 310-A8  | 8-port multiplexer expandable to 128 ports                                                                                                                 |

| 301-A8  | 8-port expansion board                                                                                                                                     |

| 301-A16 | 16-port expansion board                                                                                                                                    |

| 301-A24 | 24-port expansion board                                                                                                                                    |

| 320     | Junction panel for two connector/cable assemblies                                                                                                          |

| 322     | Connector/cable assembly for 8 ports (RS-232C)                                                                                                             |

| 322-CL  | Connector/cable assembly for 8 ports (RS-232C & current loop)                                                                                              |

| 324-N   | Interboard (Z) cable (N=number of 301 boards)                                                                                                              |

| 340-32  | External Power supply for up to 32 ports                                                                                                                   |

| 340-64  | External Power supply for up to 64 ports                                                                                                                   |

| 340-128 | External Power supply for up to 128 ports                                                                                                                  |

| 342-1   | External Power supply for RS-232C and current loop operation; number of ports serviced is 32                                                               |

| 342-2   | External Power supply for RS-232C and current loop operation; number of ports serviced is 48                                                               |

| 342-3   | External Power supply for RS-232C and current loop operation; number of ports serviced is 64                                                               |

| 342-4   | External Power supply for RS-232C and current loop operation; number of ports serviced is 128                                                              |

| 310-PS  | On-board Power Supply Option for 310-A4 or 310-A8 (Replaces external supply for RS-232C; if current loop is desired, must use 342-X external power supply) |

#### 1.1.3 MULTIPLEXER OPERATION

Each asynchronous MUX port has two data lines (incoming and outgoing) and two control lines (the outgoing device control line, and the incoming device status line). The MUX transmitter receives the data from the computer, converts it from parallel to serial form, inserts start and stop bits, inserts a parity bit if enabled, and transmits the data at the rate selected for the port to a maximum rate of 9600 baud (19.2K baud optional).

The receiver portion reverses the process. Circuitry on the MUX checks each port once per 100 microseconds for an input request. When such a request is found, the MUX reads the control words for that port and carries out the indicated operations - including access of the automatic buffer or interrupt of the computer, depending upon the conditions.

#### 1.2 SYSTEM ARCHITECTURE

The MIGHTY MUX Multiplexer interfaces from four to 128 I/O devices to a POINT 4 MARK 5/8 or Nova-type computer. The heart of the system is the POINT 4 310 board which contains all the common logic and the first eight interface ports. Each port contains the necessary control logic and buffering for full-duplex operation. The common logic contains a sequencer which interrogates the ports in turn, provides direct access to computer main memory via the DMA channel, and generates interrupts. Up to 120 more ports may be added by means of POINT 4 Data's 301 expansion boards. Each board contains 8, 16, or 24 ports. A full 128-port system requires one 310 and five 301 boards.

Figure 1-3 is a system block diagram of the MUX interface.

Figure 1-3. System Block Diagram of the MIGHTY MUX Interfacing External Devices to POINT 4 and Nova-type Computers

#### 1.3 INPUT/OUTPUT INTERFACE

The MIGHTY MUX Multiplexer is designed to operate on POINT 4 MARK 5/8 and Nova-type computers which are compatible with specifications listed below under Computer Interface. specifications are listed under Device Interface.

#### COMPUTER INTERFACE

I/O Bus POINT 4 MARK 5/8 and Nova-type

computer I/O bus-compatible

None required for 310 boards; Backplane Wiring

Z cable required for 301 boards

Device Code Jumper selectable; standard = 25

Maximum DMA Transfer Rate Data In: 900 nanoseconds/word

Data Out: 1300 nanoseconds/word

DEVICE INTERFACE

Asynchronous Transmission Type

Full Duplex, Half Duplex Line Types

Up to 9600 baud (19.2K baud Line Speeds

optional)

Line Interfaces Compatible with RS-232C/CCITT V.24

or current loop (20, 40 or 60

milliamps)

Number of Ports 128 maximum per MUX

Real Time Clock 100 Hz (period equals 10

milliseconds)

Modem Control Supports Bell 103, 200 and 300

Data Sets or equivalent

Master Terminal Mode Switch-selectable baud rate (Device Code 10/11)

up to 9600 baud (19.2K baud

optional)

#### 1.4 SPECIFICATIONS

POINT 4 Data Corporation's MIGHTY MUX Multiplexer package includes: the MUX 310 board, junction panel, connector/cable assemblies, power supplies, and a diagnostic program. Physical, electrical and environmental specifications are listed below.

#### PHYSICAL

310, 301 boards: Height:

Width: 15 in. (38.10 cm) Depth: 15 in. (38.227 cm)

Junction Panel: Height: 3-15/32 in. (8.81 cm)

Width: 19 in. (48.26 cm) Depth: 2-1/2 in. (6.35 cm)

Power Supply: Height: 3-3/8 in. (8.55 cm)

Width: 19 in. (48.26 cm) Depth: 14-1/2 in. (36.83 cm)

#### POWER REQUIREMENTS (approximate)

|         | Current  | +5    | Current           | <u>+</u> 12 |

|---------|----------|-------|-------------------|-------------|

| Model   | at +5VDC | Power | at <u>+</u> 12VDC | Power       |

| 310-A4  | 3.8A     | 19W   | .1A               | 2.4W        |

| 310-A8  | 4.0A     | 20W   | .2A               | 4.8W        |

| 301-A8  | 1.5A     | 8W    | .2A               | 4.8W        |

| 301-A16 | 2.5A     | 13W   | .4A               | 9.6W        |

| 301-A24 | 3.5A     | 18W   | .6A               | 14.4W       |

#### OPERATING ENVIRONMENT

Operating Temperature: 0 to 50 degrees C

(32 to 122 degrees F)

Relative Humidity: 0 to 90 percent noncondensing

#### 340 POWER SUPPLY (REQUIRED FOR 301 BOARDS)

Input Voltage: 115V±10%

230V model available as an option

AC Current: maximum .5A for 32 ports

Frequency: 47-440 Hz

60 Hz standard (output current

based on this)

For 50 Hz, derate output current

by 10%

BTU Per Hour: Less than 200

HM-042-0015-A INTRODUCTION POINT 4 Data Corporation 1-10 MIGHTY MUX User Manual

# Section 2 PROGRAMMING

#### 2.1 INTRODUCTION

This section outlines programming protocols for the interface of up to 128 peripheral devices via the MIGHTY MUX Multiplexer. Topics covered are: memory allocation requirements, I/O processing sequence, control word definitions, instructions for CPU control of MUX, and initialization procedures.

#### 2.2 MEMORY ALLOCATION REQUIREMENTS

To control the MIGHTY MUX, the program stores appropriate I/O command words in a certain dedicated area in memory, consisting of a control block for each port used. Memory allocation of the MUX control block and of input and output buffers is shown in Figure 2-1. All control blocks are contiguous in main memory, and may start at any multiple of 400 (octal). This starting address is under software control. In the absence of appropriate software control, the MUX control-block starting address will default to a value preset by jumpers on the MUX board. The standard for this is 36000 (octal). All control blocks must be the same size. The standard control block size is 40 words (octal); it may be jumper modified to 20 or 10 (octal).

Within each port control block (PCB), six words are used for MUX control: 0, 1, 4, 5, 6, and 7. Even-numbered words control input; odd-numbered words control output. Each set of three words contains a general control word and two pointers indicating the beginning and end of the desired buffer areas in memory. The sizes and locations of these buffers are entirely under software control. Several ports may transmit from the same buffer area at one time, since each keeps track of its own pointers. If the port is operated in single-character mode, pointer words are not read by the MUX.

MIGHTY MUX control word definitions and format are discussed in Section 2.4.

Figure 2-1. Memory Allocation for Control Block and Input and Output Buffers

#### 2.3 INPUT/OUTPUT PROCESSING SEQUENCE

In order to start the MUX, it is necessary for the program to give a DOC ac, MUX instruction. The MUX then cyclically tests all ports, checking for an input request (a character has been received) or an output request (the port is ready to accept the next output character). When one of these requests is found, the MUX stops at that port and reads its input control word (ICW) or output control word (OCW). The MUX then carries out the indicated operations, including accessing the automatic buffer, if appropriate. When all required actions for the sensed input or output request are completed, the MUX tests each port in turn. If both input request and output request are true simultaneously, input takes precedence and output is deferred until that port is inspected again. See Figure 2-2 for an I/O processing flowchart.

When an input or output process is completed (see Section 2.4.1), the MUX sends an interrupt to the CPU. An interrupt may also be given by the real-time clock on the MIGHTY MUX once each 10 milliseconds. The program, by giving a DIAS ac, MUX instruction, can then clear the interrupt and simultaneously read the MUX status word, indicating which type of interrupt was given.

Figure 2-2. Input/Output Processing Flowchart

#### 2.4 CONTROL WORD DEFINITIONS

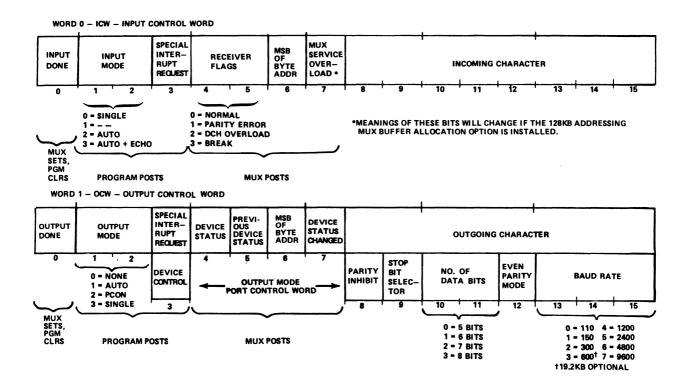

Six words are used for MUX control within each port control block: 0, 1, 4, 5, 6, and 7. The three even-numbered words control the input; the three odd-numbered words control output. In each set of three words is a general control word, with two pointers indicating the beginning and end of desired buffer areas in memory. Formats for MUX control words are shown in Figure 2-3.

#### 2.4.1 INPUT CONTROL WORD (ICW)

Table 2-1 defines the input control word (ICW), indicating each bit, its name and operation.

Figure 2-3. MIGHTY MUX Control Words

# TABLE 2-1. INPUT CONTROL WORD DEFINITIONS (WORD 0 OF EACH CONTROL BLOCK)

| Bit | Name       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Input Done | Set by MUX under the following conditions:  • If MUX is in single-character-input mode when an incoming character is received and stored in bits 8-15.  • If MUX is in automatic-input mode (with or without automatic echo) when the assigned input buffer is full; i.e., after an incoming character is placed in the byte specified by the last input byte (LIB).  • If any of the following conditions is detected by the receiver (see bits 4 and 5 below):  - Parity error - if parity inhibit is 0 (see OCW bit 8) - Data channel overload - Break (framing error)  • If MUX is in automatic-input-with-echo mode, but automatic echo was not accomplished (see bit 6 below).  • If special-interrupt request is enabled, and a special character is received (see bit 3 below).  At the same time that input-done is set, an interrupt is generated.  Input-done must be cleared by the MUX interrupt service program within one character time. If another input character is received while input-done is still set, it will override the character in bits 8-15 (automatic input is not permitted). Bit 7 is set, indicating that an incoming character has been lost, but a second interrupt is not generated. To inhibit any interrupts from a particular port, set input-done to 1. |

TABLE 2-1. INPUT CONTROL WORD DEFINITIONS (Cont) (WORD 0 OF EACH CONTROL BLOCK)

| Bit            | Name                                                        | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 & 2<br>Value | Input<br>Mode                                               | Written by the program, read by MUX to determine the type of input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0 0            |                                                             | Single-character-input-mode - each incoming character is placed in bits 8-15 of ICW, input-done is set, and an interrupt given.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0 1            |                                                             | Not used (illegal).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 0            |                                                             | Automatic-input - incoming characters are placed in the input buffer defined by input byte pointer (IBP) and last input byte (LIB), if no interrupt conditions are encountered. See bit 0 for interrupt conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 1            |                                                             | Automatic-input-with-echo - same as automatic input, except that each character placed in the input buffer is also automatically echoed (output). Note that any character producing an interrupt (other than buffer-full) is not automatically echoed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bit            |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3              | 7-Bit<br>ASCII<br>Mode -<br>Special<br>Interrupt<br>Request | Written by the program. If this bit is set, the MUX will examine each incoming character and generate an interrupt if it is a special character. The set of special characters is determined by a PROM (Programmable Read-Only Memory) on the 310 board and may be any set selected by the user. The standard set consists of all characters below octal 40 or above octal 173. Special characters are stored in ICW and produce interrupts. This allows immediate program response to such characters as backspace, carriage return and end-of-message.  A second effect of the ASCII mode bit is that the MUX sets the MSB (most significant bit) of each incoming character to one. This allows the software operating system to distinguish incoming 7-bit ASCII data characters from nondata by means of the MSB. |

TABLE 2-1. INPUT CONTROL WORD DEFINITIONS (Cont) (WORD 0 OF EACH CONTROL BLOCK)

| Bit   | Name              | Operation                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 & 5 | Receiver<br>Flags | Posted by the MUX when an input is received.                                                                                                                                                                                                                                                                                                                                                                                      |

| 0 0   |                   | Normal                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 1   |                   | Parity error - if parity is not inhibited (see OCW bit 8)                                                                                                                                                                                                                                                                                                                                                                         |

| 1 0   |                   | Data channel overload - an input character was received before the previous character from that port could be stored by the MUX. This occurs if another higher priority interface on the computer's data channel has been taking most of the computer memory cycles.                                                                                                                                                              |

| 1 1   |                   | Break, or framing error - a stop bit was not received. This is used for detecting the break character, which is a zero (0) character with no stop bit. Each of the non-normal conditions produces an interrupt and sets input-done. If more than one of these occur at the same time, only the flag with the highest number is recorded.                                                                                          |

| Bit   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6     | Not<br>Echoed     | Posted if automatic echo is not possible because output circuitry is busy with a previous output. This can only occur if the program started an output while the MUX was in automatic-input-with-echo mode. As this bit is posted, input-done is set and an interrupt generated.  If MUX Buffer Allocation option is installed, bit 6 represents the most significant bit of input buffer word address. See also effect on bit 7. |

(Table continues on next page.)

TABLE 2-1. INPUT CONTROL WORD DEFINITIONS (Cont) (WORD 0 OF EACH CONTROL BLOCK)

| Bit  | Name                       | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | MUX<br>Service<br>Overload | Set by the MUX if an input character is stored when the input-done flag is still on from a previous input. The length of time available for the MUX to service an input interrupt is approximately one character-transmission time (1 millisecond for 9600 baud data rate).  If MUX Buffer Allocation option is installed, this bit becomes a LOGICAL OR of Not-Echoed and MUX-service-overload.                                                                                                                                                 |

| 8-15 | Incoming<br>Character      | Each incoming character which produces an input-done is stored in these bits. In automatic-buffer mode, characters which are stored in the automatic buffer are not stored in ICW. However the last incoming character, which produces the buffer-full condition, is stored in both locations.  Exception: If an input buffer ends in mid-word, the byte placed in ICW is the right half of the last buffer word, and not the last incoming character. The software must therefore check for buffer-full before it checks for special-character. |

#### 2.4.2 OUTPUT CONTROL WORD (OCW)

Table 2-2 defines the Output Control Word (OCW), indicating each bit, its name and operation.

TABLE 2-2. OUTPUT CONTROL WORD DEFINITIONS (WORD 1 OF EACH CONTROL BLOCK)

| Bit | Name           | Operation                                                                                                                                                                                                                                                                 |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Output<br>Done | Set by the MUX under the following conditions:                                                                                                                                                                                                                            |

|     |                | <ul> <li>If MUX is in single-character or port-<br/>control-output mode when the output byte<br/>is read for transmission to the port.<br/>If output control words are reloaded<br/>within 1-2 character times,<br/>uninterrupted output will result.</li> </ul>          |

|     |                | <ul> <li>If MUX is in automatic-buffer mode when<br/>the last byte of the automatic buffer is<br/>read for transmission. If the output<br/>control words are reloaded within 1-2<br/>character times, uninterrupted output<br/>will result.</li> </ul>                    |

|     |                | <ul> <li>If MUX is in automatic-output-with-<br/>special-interrupt-request mode, and if<br/>the transmitted character is a special<br/>character, automatic output is<br/>terminated after transmitting the<br/>special character.</li> </ul>                             |

|     |                | <ul> <li>If the device-status-changed bit (bit 7)<br/>becomes a one (1), regardless of output<br/>mode.</li> </ul>                                                                                                                                                        |

|     |                | At the same time that output-done is set, an interrupt is generated. Output-done must be cleared by the program before another output can take place on that port. Leaving output-done set inhibits further interrupts from that port, even if the device status changes. |

TABLE 2-2. OUTPUT CONTROL WORD DEFINITIONS (Cont)

(WORD 1 OF EACH CONTROL BLOCK)

| Bit   | Name                            | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 & 2 | Output<br>Mode                  | Written by the program and read by MUX to determine the type of output.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0 0   |                                 | No output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0 1   |                                 | Automatic-buffer output - MUX will output<br>from the automatic buffer defined by<br>output byte pointer (OBP) and last output<br>byte (LOB).                                                                                                                                                                                                                                                                                                                              |

| 1 0   |                                 | Port-control-output - the data in bits 3 and 8-15 are sent to the port as control data for assigned control functions.                                                                                                                                                                                                                                                                                                                                                     |

| 1 1   |                                 | Single-character-output - the data byte in bits 8-15 is sent to the port for transmission to the external device.                                                                                                                                                                                                                                                                                                                                                          |

| Bit   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3     | Special<br>Interrupt<br>Request | If output mode = 01 (auto): Written by the program; if this bit is set to one (1), the MUX will test each outgoing character to determine if it is a special character. If it is, the MUX will transmit it, set output-done, produce an interrupt, and terminate automatic output. This bit is useful in driving printers which require special service after a carriage return character, such as a line feed, delay time, or a print line command.                       |

|       | Device<br>Control               | If output mode = 10 (port control output): Written by the program; transferred by the MUX to the port when the port-control- output is done. This bit is stored by a flip-flop in the port circuitry and applied as an EIA level on the device- control line to an external device. It may be used for any desired function.  1 = +10V = EIA Positive = function on 0 = -10V = EIA Negative = function off  If output mode = 00 (none) or 11 (single) bit 3 has no effect. |

TABLE 2-2. OUTPUT CONTROL WORD DEFINITIONS (Cont)

(WORD 1 OF EACH CONTROL BLOCK)

| Bit | Name                         | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | Device<br>Status             | Written by the MUX each time OCW is inspected. This is the current value of the device-status line from the external device. This line may also be used for other desired functions; it does not interact with the port in any other way.  1 = EIA Positive, i.e. > +3V  0 = EIA Negative, i.e. ≤ 0V or open  Note: Any voltage above +1.3 volts will produce a 1; any voltage below +0.7 volts will produce a 0; the result of voltages between these limits is indeterminate. |

| 5   | Previous<br>Device<br>Status | Written by the MUX each time OCW is inspected. The value read from Bit 4 is rewritten here. It is of no significance to the programmer.                                                                                                                                                                                                                                                                                                                                         |

| 6   | Unused                       | Set to 0 by the MUX if MUX Buffer Allocation option is not installed. If MUX Buffer Allocation option is installed, bit 6 represents the most significant bit of output buffer word address.                                                                                                                                                                                                                                                                                    |

| 7   | Device<br>Status<br>Changed  | Written by the MUX when the device-status line does not equal the device-status bit (bit 4). When this bit is set, bit 0 (output-done) is also set, and an interrupt is generated.                                                                                                                                                                                                                                                                                              |

(Table continues on next page.)

TABLE 2-2. OUTPUT CONTROL WORD DEFINITIONS (Cont) (WORD 1 OF EACH CONTROL BLOCK)

| Bit        | Name                  | Operation                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8-15       | Outgoing<br>Character | If output mode is set to ll (single character), this byte is sent to the port for transmission to the external device.                                                                                                                                                                                                                                                                           |

|            |                       | If output mode is set to 00 or 01 (inactive or automatic), this byte is ignored. In automatic-output-with-special-interrupt request, this byte must not be a special character; otherwise the special character detection logic will not permit automatic output to start. When an output-done interrupt is produced, the MUX will store the character that produced the interrupt in this byte. |

|            |                       | If output mode is set to 10 (port control output), this byte is sent to the port as a control character, governing both output and input. In this case, the meanings of the eight bits are as follows:                                                                                                                                                                                           |

| 8<br>Value | Parity<br>Inhibit     |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0          |                       | Parity is generated (transmit) and checked (receive).                                                                                                                                                                                                                                                                                                                                            |

| 1          |                       | No parity                                                                                                                                                                                                                                                                                                                                                                                        |

| Bit        |                       |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9          | Stop Bit<br>Selector  |                                                                                                                                                                                                                                                                                                                                                                                                  |

| Value      | beleetol              |                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0          |                       | One stop bit.                                                                                                                                                                                                                                                                                                                                                                                    |

| 1          |                       | Two stop bits (output). For input, one stop bit is adequate.                                                                                                                                                                                                                                                                                                                                     |

TABLE 2-2. OUTPUT CONTROL WORD DEFINITIONS (Cont) (WORD 1 OF EACH CONTROL BLOCK)

| Bit                       | Name           | Operation                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 10,11 Number of Data Bits |                | This field governs the data bits only; parity (if not inhibited) is an additional bit. If less than eight bits are selected, the character is right justified and the unused most significant bits are set to zero on input. For output, the character must be right justified, but the unused most significant bits are ignored. |  |  |  |  |  |

| Value                     |                |                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 0 0                       | ·              | 5 bits                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 0 1                       |                | 6 bits                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 1 0                       |                | 7 bits                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 1 1                       |                | 8 bits                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Bit                       |                |                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 12                        | Parity<br>Mode | In effect if bit 8 is set to 0.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

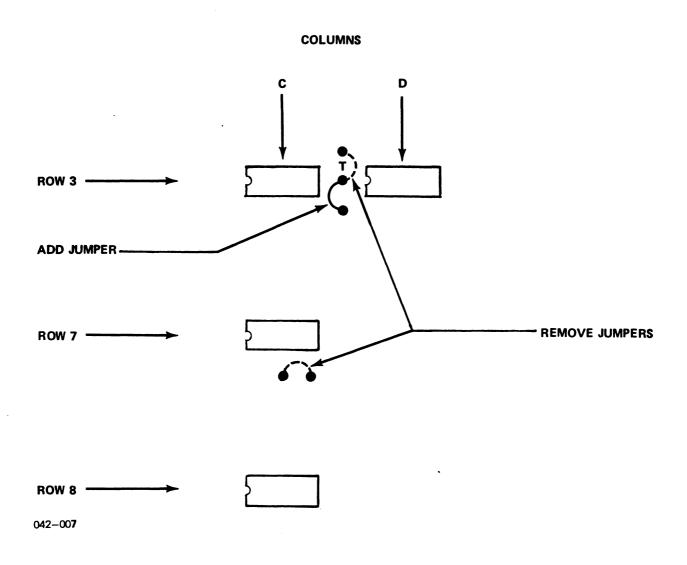

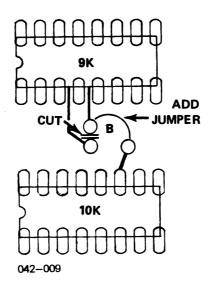

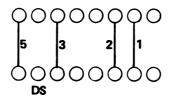

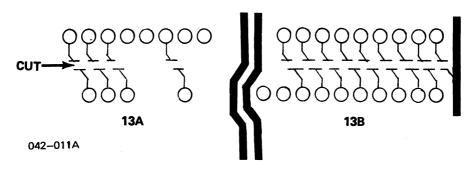

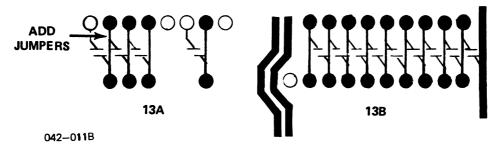

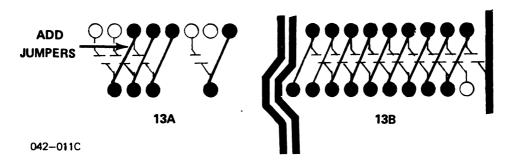

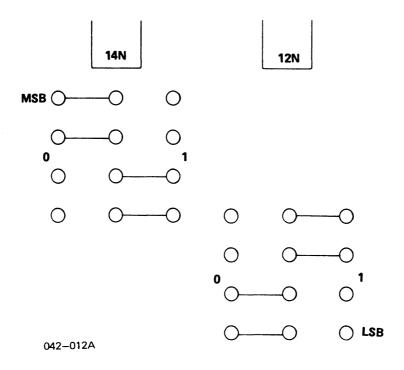

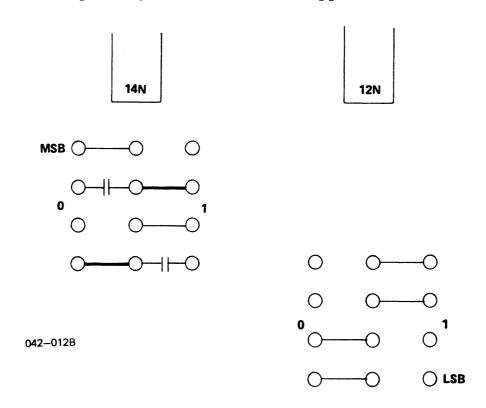

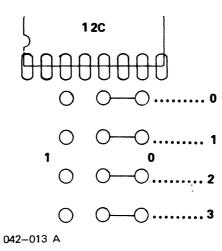

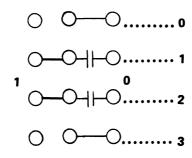

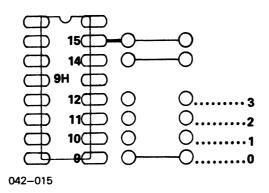

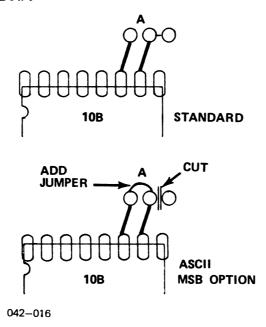

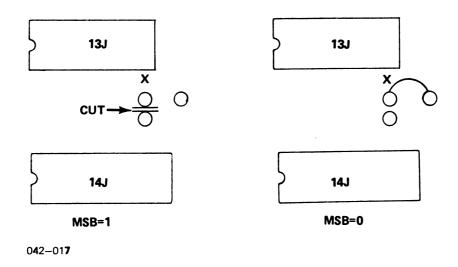

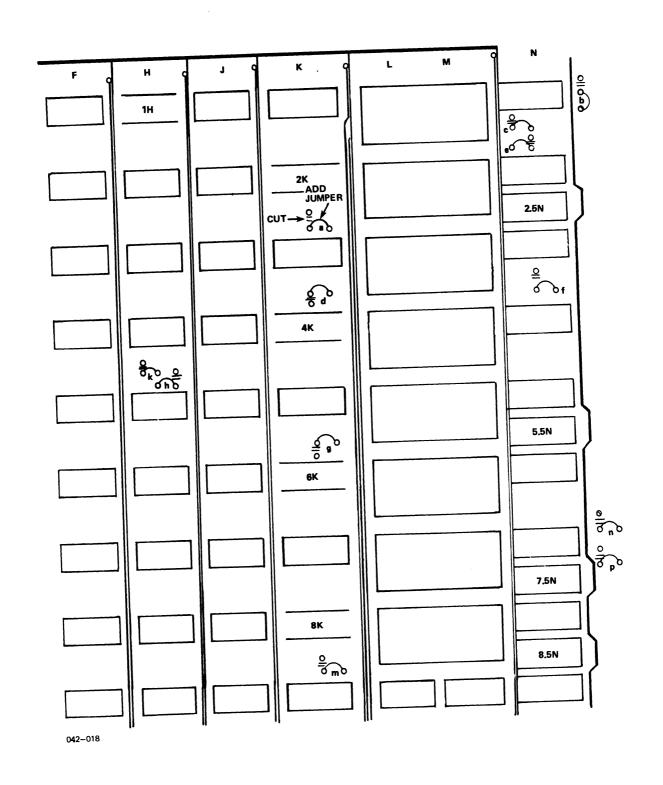

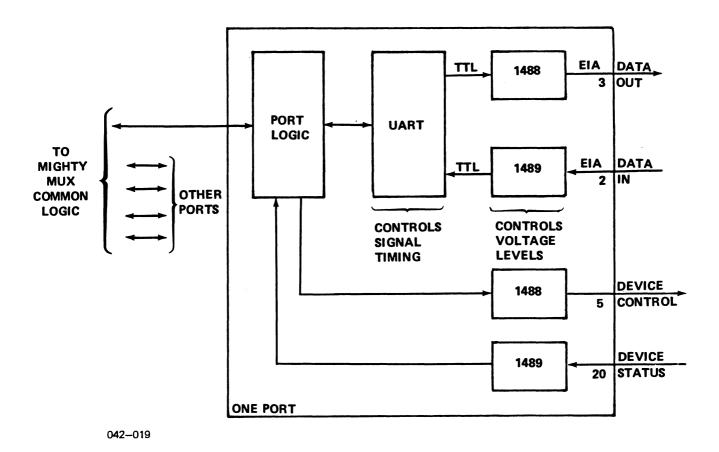

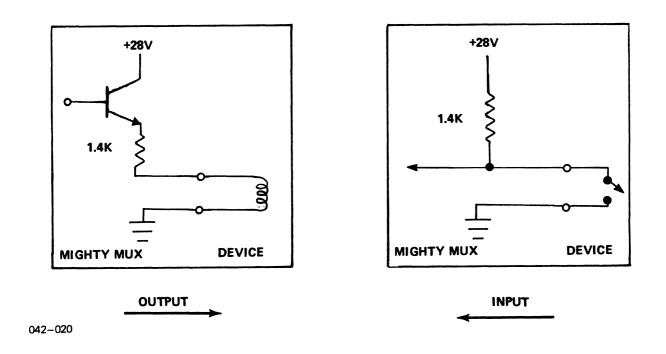

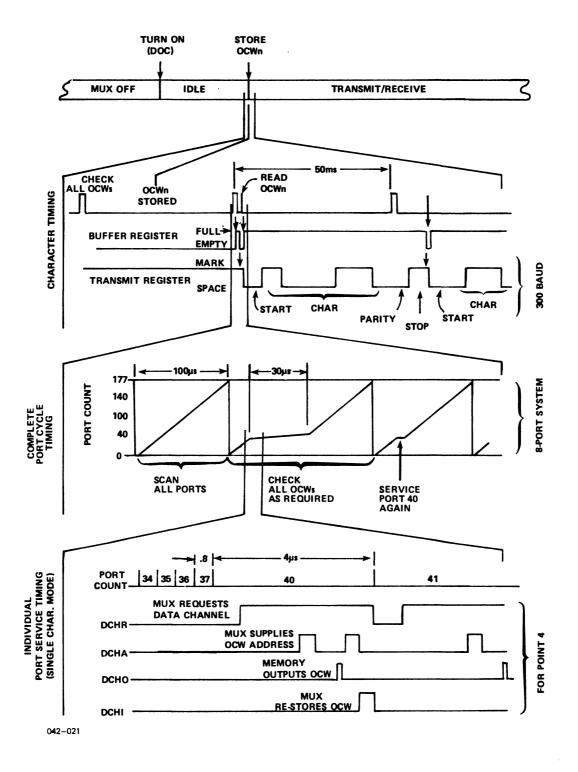

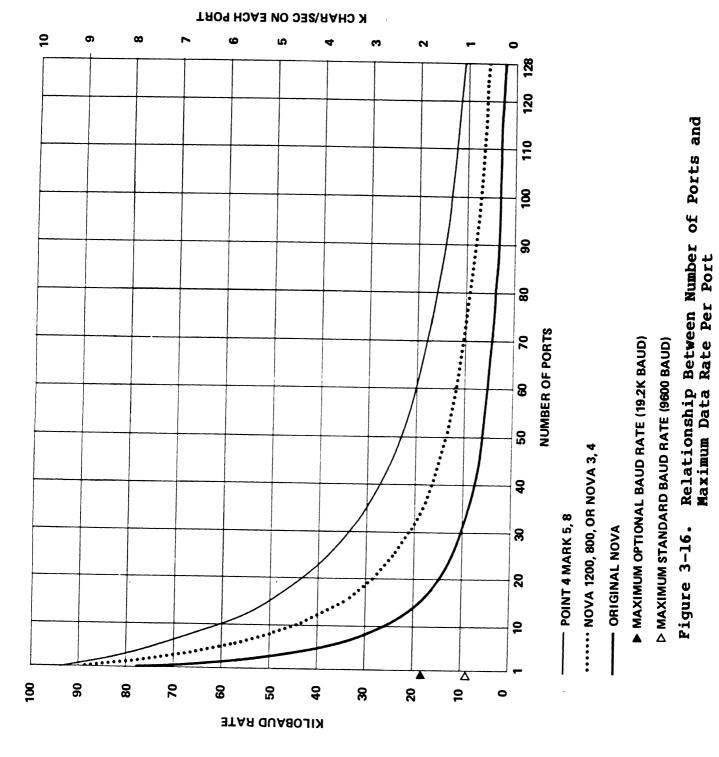

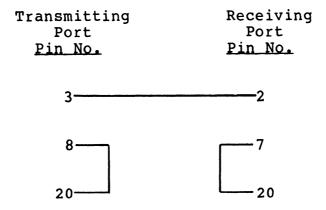

| <u>Value</u>              |                |                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |