# Model 750-IPC

# Foreground/Background Interface

Copyright 1991.

All rights reserved. No material herein may be reprinted, copied or otherwise reproduced without permission from ZETACO.

> 600-0538-00 Revision: A

# TABLE OF CONTENTS

| SECTION 1 | INTRODUCTION            |

|-----------|-------------------------|

| SECTION 2 | INSTALLATION            |

| SECTION 3 | CONFIGURATION (OPTIONS) |

| SECTION 4 | PROGRAMMING NOTES       |

| SECTION 5 | SPECIFICATIONS          |

| SECTION 6 | DIAGNOSTICS             |

# 1.0 INTRODUCTION

The 750-IPC controller is a single board controller which allows the generation of interrupts under software control for the purpose of expediting the transition between RDOS Foreground and Background. The 750-IPC also provides 16 bit DOA/DIA registers at both the even and odd device codes which can be loaded and read under software control.

Features of the 750-IPC includes:

- 1) Selection of any Even, Odd Device Code Pair (i.e. 2,3 or 40,41 or 76,77).

- 2) Selection of any Mask Bits (Data 0 through Data 15).

The controller occupies one slot in the CPU chassis.

# 2.0 INSTALLATION INSTRUCTIONS

# 2.1 UNPACKING

Upon receiving the Interface Package, unpack the contents and inspect the board for visual damage. The package contains:

- 1) Controller Board

- 2) Manual

- 3) Diagnostic Tape

If any damage is apparent, do not attempt to install the controller, but notify the Shipper and Zetaco immediately.

#### <u>2.2</u> <u>BOARD INSTALLATION</u>

The controller board may be installed in any General I/O, Memory I/O or I/O Only slot of the Data General Nova or Eclipse Minicomputer.

Verify the Device Code and Mask Bit selections are correct (these are Switch Selectable).

Install the controller in the desired slot, component side up, and lock into position with the release levers.

If with the selection of the I/O slot, a vacant slot or slots exist between the controller and the board below it, the DCHP (Data Channel Priority) and the INTP (Interrupt Priority) signals must be physically jumpered on the computer backpanel to maintain priority interrupt continuity. Install one end of a wire-wrap jumper to the DCHP-OUT signal at Pin 93 of the "A" connector occupied by the device below the controller. Connect the remaining end to the DCHP-IN signal at Pin 94 of the "A" connector occupied by the controller, bridging the vacant slot or slots. Similarly, connect the INTP-OUT signal (Pin A-95) from the lower device to the INTP-IN signal at Pin A-96 of the controller. This will complete the priority interrupt continuity to the card. If vacant slots exist between the controller and the device above the controller, perform similar strapping of the DCHP and INTP signals to maintain interrupt priority.

CAUTION: Be sure NO existing cabling or devices are connected to the backplane of the slot the 750-IPC is to be installed in.

# 3.0 CONFIGURATION (OPTIONS)

# <u>3.1</u> <u>DEVICE CODE SELECTION</u>

The five position switch at location D2 selects the Even Device Code of the required Even-Odd Device Code Pair. use the Table to set the desired Device Code.

#### DEVICE CODE TABLE

|             | (DS0)    | (DS1) | (DS2) | (DS3) | (DS4) |

|-------------|----------|-------|-------|-------|-------|

| DEVICE CODE | S1       | S2    | S3    | S4    | S5    |

| 0X          | ON       | ON    | ON    | -     | -     |

| 1X          | ON       | ON    | OFF   | -     | -     |

| 2X          | ON       | OFF   | ON    | -     | -     |

| 3X          | ON       | OFF   | OFF   | -     | -     |

| 4X          | OFF      | ON    | ON    | -     | -     |

| 5X          | OFF      | ON    | OFF   | -     | -     |

| 6X          | OFF      | OFF   | ON    | -     | -     |

| 7X          | OFF      | OFF   | OFF   | -     | -     |

| X(0 & 1)    | -        | -     | -     | ON    | ON    |

| X(2 & 3)    | <u>-</u> | -     | -     | ON    | OFF   |

| X(4 & 5)    | -        | -     | -     | OFF   | ON    |

| X(6 & 7)    | -        | -     | -     | OFF   | OFF   |

|             |          |       |       |       | 1     |

- = Don't care

Switch is shown with Position 2, 3, 4 and 5 ON which equals Device Code Selection of 40, 41.

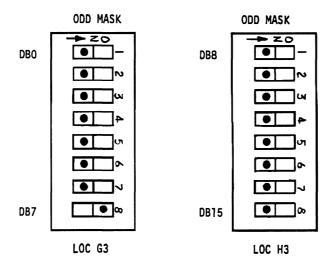

#### 3.2 MASK BIT SELECTION

Switches at Location J3 and K3 select 1 of the 16 possible Mask Bits associated with the Even Device Code and switches at Locations G3 and H3 select 1 of the 16 possible Mask Bits associated with the Odd Device Code. Only one switch position can be ON for the J3, K3 Mask Bit Select Switches, and only one switch position can be ON for the G3, H3 Mask Bit Select Switches. See drawing for further definition.

DBO = Data Bit 0, DB15 = Data Bit 15, Mask Bit 7 shown selected

# 4.0 PROGRAMMING NOTES

The Model 750 Inter-Program Communications Device is used with Data General RDOS to provide a software controlled signal between the foreground and background partitions for the purpose of indicating without delay the completion of any task.

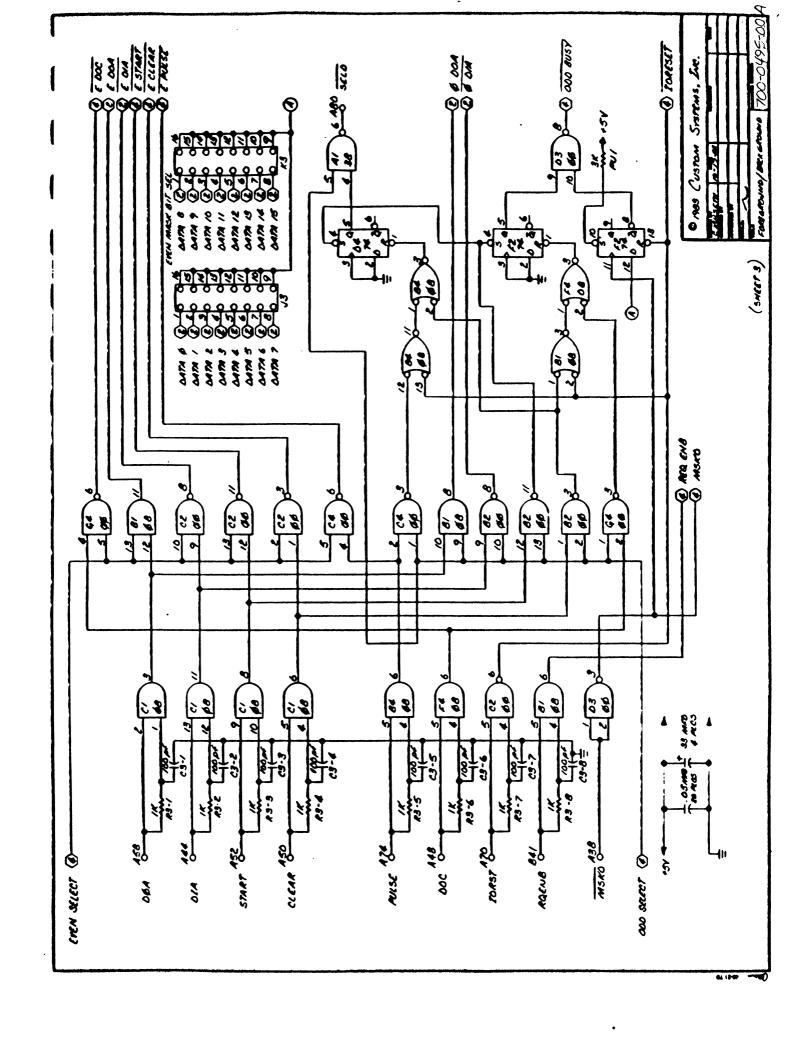

The Device is an I/O Interrupt Generating Device. The Start Command initiates the interrupt sequence, and the Clear Command clears the interrupt. The following Instruction Formats explain the Commands and what results are achieved.

.DOA XX Load Register (Even or Odd Device Code).

Load Bits 0 to 15 into Load Register.

.DIA XX Read Register (Even or Odd Device Code)

Read Bits 0 to 15 from Register. DIA reads what DOA Command stored in the Register.

#### .START (ODD DEVICE CODE)

- a) Sets Odd Done F/F

- b) Sets Odd INTR F/F

- c) Sets the INTR F/F if not Masked

An INTA command returns Bits 10 through 15 (Device Code) of the Interrupting Device, initiated by the Start Command.

#### .START (EVEN DEVICE CODE)

- a) Sets the Even Busy F/F

- b) Sets the Even INTR F/F

- c) Sets the INTR F/F if not Masked

An INTA Command returns Bits 10 through 15 (Device Code) of the Interrupting Device, initiated by the Start Command.

#### .CLEAR (ODD DEVICE CODE)

- a) Clears Odd Done F/F

- b) Clears Odd INTR F/F

#### .CLEAR (EVEN DEVICE CODE)

- a) Clears Even Busy F/F

- b) Clears Even INTR F/F

# .PULSE (ODD DEVICE CODE)

a) Clears Odd Done F/F

#### .PULSE (EVEN DEVICE CODE)

a) Clears Even Busy F/F

#### .DOC (ODD DEVICE CODE)

a) Clears Odd INTR F/F

#### .DOC (EVEN DEVICE CODE)

a) Clears Even INTR F/F

#### .IORST

- a) Clears Odd, Even Mark F/F

- b) Clears Odd Done F/F, Even Busy F/F

- c) Clears Odd INTR F/F, Even INTR F/F

# **5.0 SPECIFICATIONS**

Power Requirements:

Power is supplied by the minicomputer power supplies. The board requires only +5 Volt DC.

+5 VDC Current = 1 Amp

**Environmental:**

Operating Temperature

Operating Humidity

Non-Operating Temperature

Non-Operating Humidity

10 C to 40 C degrees 10% to 90% non-condensing -40 C to 55 C degrees 10% to 90%

# <u>6.0</u> <u>DIAGNOSTICS</u>

A diagnostic tape is provided with the 750-IPC which contains a stand-alone diagnostic to test the controller board.

In order to run the diagnostic:

- 1) Boot the support tape and select the diagnostic from the menu.

- 2) The diagnostic will prompt you for input. Enter the even device code and the even and odd device code mask bit numbers that were configured per sections 3.1 and 3.2.

- The diagnostic will display "Testing..." and report PASS upon completion. Any errors encountered will be displayed on the screen.

FOREGROUND/BACKGROUND

CONTROLLER

1. NUMBERS FOUND MIPHIN THE NEADON STABOLS INDICATE SULETS WHERE CONTINUED LODIC WILL BE FOUND EXAMPLE: (2) - SUEET B

NOTE

SNEET 1 OF 4

O1983 SLSTOM STSTEMS, INC

100.001 amajonaj kanagas

1154